如今,半导体行业处于技术创新的前沿,彻底改变了人工智能 (AI)、5G 通信和高性能计算 (HPC) 等各种应用。随着我们进入生成式人工智能时代,对更强大、更紧凑、更高效的电子设备的需求不断增长。

在这一追求中,先进封装已成为关键的推动者,在超越摩尔时代至关重要。本文将深入探讨先进封装平台的定义以及它们如何塑造半导体的未来。

先进封装 (AP) 是指封装集成电路 (IC) 以提高性能的多种创新技术。

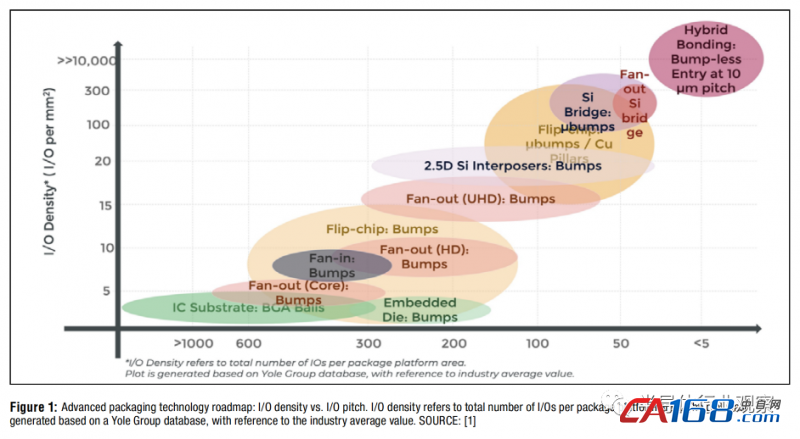

与传统封装方法相比,根据目标应用的要求、性能和成本,采用不同的 I/O 密度和/O 间距,可以增强功能、提高性能并提供附加值(图 1)。按照我们的划分 ,我们考虑以下 AP 平台:扇出 (FO) 型封装、晶圆级芯片规模封装 (WLCSP)、倒装芯片球栅阵列 (fcBGA)、倒装芯片 CSP (fcCSP)、系统级封装 (SiP) 和 2.5D/3D 堆叠封装。此外,还包括使用混合接合的互补金属氧化物半导体 (CMOS) 图像传感器 (CIS)、高带宽存储器 (HBM)、3D 堆叠 动态随机存取存储器 (DRAM) (3DS)、3D 片上系统 (3D-SoC)、3D NAND、硅中介层(Si interposers)和嵌入式硅桥(embedded Si bridges)等等。

AP 的重要性怎么强调都不为过,尤其是在新兴技术和应用的背景下。以下部分介绍了推动 AP 需求的主要驱动因素。

人工智能和机器学习:人工智能应用程序需要低延迟的高性能计算。2.5D/3D 堆叠封装、HBM 和 Si 中介层等 AP 平台可实现更高的内存带宽和改进的系统集成,这对于 AI 推理和训练任务至关重要;

生成式人工智能时代:生成式人工智能时代强调人工智能模型自主创建新数据、内容或解决方案的能力。这个时代需要能够实时处理大量数据并生成复杂算法的高效硬件,而 AP 技术使这成为可能;

5G通信:5G 技术的推出需要紧凑、高效的设备来适应复杂的通信系统。WLCSP 和扇出封装等 AP 解决方案可实现更小的外形尺寸、更低的功耗和改进的热管理,使其成为 5G 设备的理想选择;

HPC:数据中心和超级计算机等 HPC 应用程序需要快速可靠的处理。fcCSP 和 FCBGA 等技术提供卓越的电气性能和更高的 I/O 密度,使其非常适合 HPC 系统;

探索先进封装平台

以下部分描述了主要的先进封装平台。

一、FO 封装

FO封装包括三大类:核心扇出型(core fan-out)、高密度扇出型(high-density fan-out)和超高密度FO型(ultra highdensity FO)。核心扇出封装消除了对引线键合或倒装芯片互连的需求,从而提供了改进的 I/O 密度、增强的电气性能和高效的热管理;高密度 (HD) FO 进一步采用了相同的概念,采用先进的重新分布层 (RDL) 和互连结构来实现更高的 I/O 密度;超高密度 (UHD) FO 使用更细间距和更高密度的多层 RDL,以在紧凑封装内提高组件集成度、更大带宽和高级功能。UHD FO 通常应用于较大的封装和多芯片集成,使用 IC 基板来弥合扇出封装和印刷电路板 (PCB) 之间的间隙。

二、晶圆级芯片级封装 (WLCSP)

WLCSP 涉及将 IC 直接封装在晶圆上,从而消除了单独的芯片分割和封装步骤。WLCSP 具有紧凑的外形尺寸、增强的电气性能和成本效率,使其成为尺寸、重量和性能至关重要的移动设备和可穿戴设备的理想选择。

三、fcBGA/CSP

这些技术涉及使用焊料微凸块或铜柱将 IC 正面朝下直接安装到有机基板上。与传统引线键合技术相比,倒装芯片 BGA/CSP 解决方案提供更小的占地面积、更短的互连路径、更高的 I/O 密度以及更高的电气性能。这些特性对于服务器、游戏机和网络设备等 HPC 应用尤其重要。

四、2.5D/3D堆叠封装

2.5D/3D 堆叠封装涉及垂直堆叠多个裸片或芯片,形成三维结构。该平台可实现更高的集成度、更高的性能和更小的外形尺寸,使其成为应对人工智能、5G 和 HPC 应用挑战的重要技术。2.5D/3D 堆叠封装中的具体应用包括使用混合键合技术的 CIS、用于更快数据访问和改进内存带宽的 HBM、用于高度集成系统的 3D-SoC 以及用于提高存储密度和容量的 3D NAND。

五、系统级封装 (SiP)

SiP 是一种将多个 IC 或“小芯片”集成到单个模块中的 AP 类型。这些小芯片可以包括各种组件,例如处理器、存储器、射频 (RF) 收发器和电源管理 IC 在封装内互连。这种高集成度允许将完整的功能系统包含在单个封装内,使 SiP 成为节省空间的解决方案,非常适合外形尺寸和集成度至关重要的应用,例如移动设备和可穿戴设备。SiP 还在设计和制造方面提供了显着的灵活性,因为每个小芯片都可以使用最适合其功能的工艺技术来制造。

市场份额和行业重点

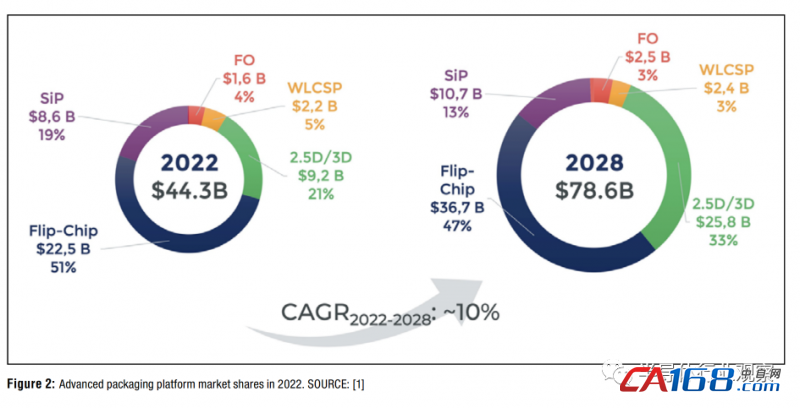

由于对先进解决方案的需求不断增长,AP 平台市场正在经历显着增长。如图 2 所示,2022 年 AP 市场预计为443亿美元,划分如下:倒装芯片占据 51% 的市场份额,其次是 2.5D/3D,占据 21% 的市场份额——受到AP平台的推动,预计到2028年,这将是增长最快的领域。SiP 预计将占据 19% 的市场份额,其次是 WLCSP 和 FO 封装,分别占据 5% 和 4% 的市场份额。

在主要参与者中,外包半导体封装和测试(OSAT)公司以及主要集成设备制造商(IDM)和代工厂,如台积电、英特尔和三星,正在大力投资高端封装解决方案,重点是2.5D /3D堆叠封装。

作为IDM,英特尔一直在积极投资AP技术。英特尔在其产品中采用嵌入式多芯片互连桥 (EMIB) 和 Foveros 等 AP 技术,并为客户提供代工和封装服务。该公司对创新和垂直整合的高度重视使其成为 AP 领域的重要参与者。

全球半导体代工厂领导者台积电通过其 3DFabric平台提供 AP 服务,该平台采用集成扇出 (InFO)、晶圆基板上芯片 (CoWoS) 和 3D 集成系统等技术芯片 (TSMC-SoIC)。该公司提供全面的晶圆到封装解决方案,涵盖晶圆前端制造、晶圆级工艺、封装和基板上组装。台积电与ASE、SPIL、Amkor等封装公司合作,巩固了其在AP市场的主导地位。

作为全球最大的 OSAT 企业,日月光专注于 AP 技术,包括倒装芯片、扇出和 SiP 解决方案。公司与英特尔、台积电等领先半导体公司的合作,公司还强调其在推动 AP 技术进步方面的关键作用。

Amkor 是半导体封装和测试行业的重要参与者,提供多种 AP 解决方案。其中包括晶圆级封装 (WLP)、2.5D/3D 封装、倒装芯片和 SiP 解决方案。Amkor 凭借广泛的 AP 产品组合,仍然是快速发展的先进封装市场的主要竞争者。

作为 IDM 企业,三星在 AP 市场拥有强大的影响力,提供 WLCSP、SiP 和异构集成 (H I) 技术等解决方案。三星利用其扇出面板级封装 (FOPLP)、倒装芯片、引线键合和 3D 堆叠封装能力来封装其加速处理单元 (APU) 和内存,但它也将生产外包给 ASE、Amkor、和 PTI。三星还开始为谷歌的 Tensor G2 和百度的 I-CubeS 制造 FOPLP。

异构和小芯片:彻底改变AP路线图

异构和小芯片代表了半导体设计和封装的范式转变。异构概念涉及结合不同的材料、工艺和设备来创建一个统一的系统。这种方法可以将多种功能小芯片无缝集成在单个封装上,从而释放半导体设计和制造的新可能性。

另一方面,Chiplet 是异构的一个基本方面。根据我们在 Yole 的定义,小芯片方法代表了一种新兴的半导体设计理念,它将两个或多个分立芯片组合在分解的 SiP 设计中。与可能的单片替代方案相比,小芯片提供了更大的设计灵活性、更快的上市时间、更高的良率和经济效益。小芯片的功能涵盖典型处理器 SoC 中的基本知识产权 (IP) 块,包括中央处理单元 (CPU)、图形处理单元 (GPU)、神经处理单元 (NPU)、I/O 和内存控制器以及接口、高速缓存存储器和模拟功能(SerDes、PLL、DAC、ADC、PHY 等)。

混合键合:弥合异构领域的差距

混合键合是一项新技术,可以实现半导体器件的垂直堆叠,从而可显著提高器件的性能、功能和可靠性。它是异构的关键推动者,可在键合过程中提供卓越的精度和可靠性。混合键合可确保小芯片之间牢固可靠的连接,从而增强它们在先进封装平台中的集成。这项技术开启了半导体设计的新可能性,使得开发曾经被认为不可能的尖端解决方案成为可能。

混合键合是一项尖端技术,可实现多种芯片架构,满足 HPC、人工智能、服务器和数据中心等高端应用的需求。随着该技术的成熟,受益于高性能芯片间连接,预计将进一步扩展到消费类应用、存储设备以及移动和汽车应用。异构的概念正在推动封装技术的创新,以满足特定的性能、尺寸、功耗和成本要求。混合键合成为高端异构应用的可行途径,将微小的铜焊盘嵌入电介质中,形成电介质到电介质和金属到金属的键合。这种接合技术具有许多优点,例如显着增加的 I/O 连接、最小的信号延迟、扩展的带宽、更高的存储密度以及改进的功率和速度效率。

图 3 所示的 AP 技术路线图展示了十年来四个关键要素在小型化和增加密度方面取得的有趣进展:3D 堆叠间距(3D stack pitch)、凸块 I/O 间距(bump I/O pitch)、RDL 线/空间(RDL line/space)和球 I/O 间距( ball I/O pitch)。3D 堆叠间距凸显了混合键合方法(晶圆到晶圆、裸片到晶圆以及裸片到裸片)小型化的明显趋势。通过晶圆到晶圆,我们观察到从 2019 年的 2μm 到 2029 年预计的 0.8μm–0.5μm 的显著减小。这代表了在减小间距尺寸方面取得的重大成就,这可能会实现更多组件的集成,并有可能增强表现。

同样,裸片到晶圆混合键合预计将从 2022 年的 10μm 缩小到 2029 年的 6-4.5μm。这也表明将推动更高密度的封装,从而生产更小、更高效的设备。然而,间距尺寸的减小速度似乎比晶圆间键合稍慢,反映出部署该技术时面临的一些挑战。

尽管在时间轴上出现较晚,但裸片到裸片混合键合将大幅减小,从 2023 年的40μm–10μm 减少到 2029 年的 10μm–6μm。间距尺寸的显著下降可能反映了这种方法的快速进步,这可以提供 高密度封装的替代途径。

对于凸点 I/O 间距,2019 年至 2023 年间,从 80μm–40μm 大幅减少。然而,到 2029 年的接下来几年,减小趋势放缓,间距范围在 50μm至 40μm 之间。这种停滞状态可能表明技术正在达到其物理极限或遇到制造挑战。RDL 线/空间预计将缩小,从 2019 年的小于 5/5μm 减少到 2029 年的小于 2/2μm。这种尺寸更小的一致趋势意味着对更高密度互连和更紧凑封装设计的推动。从而提高性能。最后,球 I/O 间距表现出卓越的一致性,在十年内保持 300μm 的尺寸。这种稳定性可能表明技术成熟且优化。

总结

先进封装已成为半导体行业进步的关键,为人工智能、5G 和 HPC 铺平了道路。多样化的 AP 平台,包括扇出封装、WLCSP、fcBGA/CSP、SiP 和 2.5D/3D 堆叠封装,加上异构和小芯片的变革潜力,正在重塑半导体格局。

随着生成式人工智能时代的展开,AP技术将继续推动创新,实现更小、更强大的电子设备,推动我们进入充满无限可能的未来。半导体行业将继续发展,而 AP 将保持领先地位,释放新功能并塑造明天的技术。

随着 AP 技术的不断进步,可以预见更多突破性的应用程序和解决方案将在未来几年重新定义我们与技术交互的方式。该路线图体现了 AP 技术的演变,突出了小型化和密度增加的明显趋势。然而,它也强调了创新停滞不前的领域,表明未来需要突破或替代方法。