英特尔今天在美国举行的 IEDM 会议上展示了使用背面电源触点将晶体管缩小到 1 纳米及以上的关键技术。

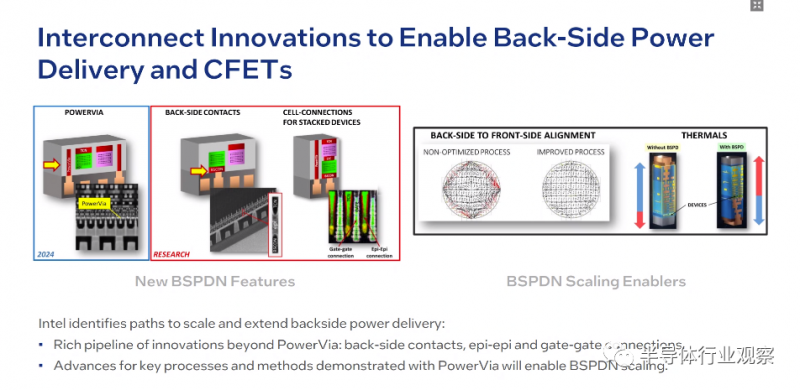

Intle已经展示了背面电源通孔,从晶圆背面连接电源轨,这将在Intel 18A 1.8nm工艺技术中实现。背面电源触点将能够缩小至 1 纳米及以上。

“我们非常高兴成为第一个在intel 18A 工艺中实现背面电源通孔的公司,”Components Research 芯片中尺度工艺开发总监 Paul Fisher 说道。

这是堆叠带状晶体管下一步的关键部分。

“在 IEDM 上,我们将提供电源通孔之外的全面描述,”Intel 院士兼技术开发总监 Mauro Kobrinsky 说道。

“在背面供电处理器之前,内置有多层金属线。摩尔定律驱动更多的晶体管,这驱动更多的层和更小的电线,从而增加了复杂性和成本。每一层都必须提供信号和电源线路,这通常会导致优化妥协和资源竞争、互连瓶颈,这变得越来越具有挑战性。”

“背面电源从根本上改变了这种情况,通过设备两侧的互连和垂直互连,通过适当的电源。我们明年能够在intel 20A 和intel 18A 中部署这项技术,这意味着正面的电线更少,这样我们就可以放宽间距,不再需要做出优化妥协,”他说。

“通过我们的研究,除了电源之外,还涉及背面接触,这使我们首次能够从设备的两侧连接晶体管。我们已经能够在我们的研究车辆中制造这些触点,并且正面和背面触点相匹配,而无需使用电源过孔进行布线。这使我们能够降低电池的电容,从而以更低的功耗获得更高的性能,”他说。

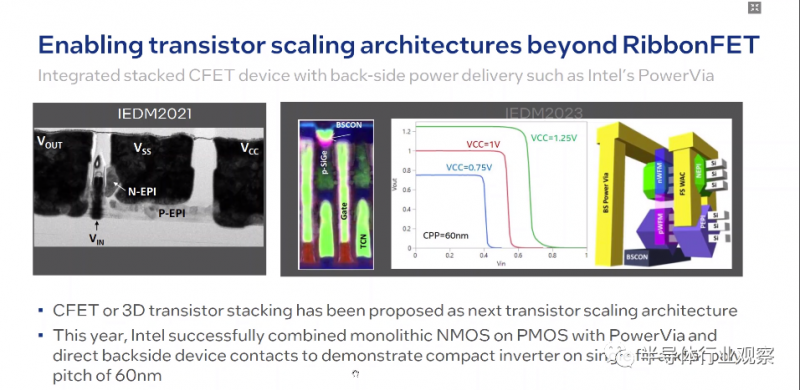

英特尔已使用这种互连技术将晶体管与 NMOS 器件堆叠在带状 PMOS 之上,以构建反相器门。

“这对电源和信号同时产生了一个有趣的挑战,包括背面接触和电源过孔。有意义的堆叠过程不仅需要能够堆叠设备,而且还需要以节省空间的方式互连它们。如果互连增加了占位面积,我们就会失去我们试图实现的晶体管密度的影响,因此必须具有低占位面积、背面接触和电源通孔,而堆叠栅极连接是实现这一点的关键,”他说。

堆叠中的下部晶体管连接到晶圆的背面,顶部晶体管连接到顶部,同时通过堆叠连接。这避免了在堆栈顶部需要更多触点。关键的一步是,英特尔确认使用背面接触不会影响热行为,因此随着时间的推移,标准的热改进会随着时间的推移而扩展。

“这使我们第一次能够对齐晶圆正面和背面的特征,并且我们已经确定了正面到背面对齐的多个路径。我们在实现这种叠加方面做出了重大改进。这对于实际的设备堆叠实施至关重要,”他说。

堆叠式 CFET 互补器件采用可扩展的工艺构建。

英特尔首席工程师 Marko Radosavljevic 表示:“我们的晶体管缩放和互连工作之间存在巨大的协同作用,因为我们希望最大限度地提高密度。”

“如果没有背面接触,我们将需要额外的顶部接触,这会增加占地面积。我们在规模更大的研究车辆上将背面接触与器件堆叠结合起来,其多晶硅节距为 60 纳米,与我们在 2021 年展示的工作相比,其规模相当大。”他说。

英特尔已将堆叠晶体管用于单个鳍上的逆变器门

“我们有三个带,nmos 和 pmos 各三个,我们必须弄清楚如何创建 pn 结,”Radosavljevic 说。“这是一项新颖的技术,我们需要扩展到垂直图案化技术,以便在堆栈的顶部或底部进行操作,并且我们需要单独的连接。我们使用电源通孔将顶部器件连接到晶圆背面,并使用背面电源触点连接底部器件。我们使用门控制器将门连接在一起。”

“inverter 需要连接晶体管的源极,我们使用顶部的环绕式接触,以一种节省空间的方式将顶部器件连接到底部器件,而不是绕过器件,我们将在硅上面。”

“inverter 是我们可以创建的最简单的电路,它是在同一个晶体管中创建的,具有器件堆叠以及电源通孔和背面接触。我们对这项研究的前景感到非常兴奋,因为这是未来设备密度的显着提高,”他说。