大约一年前,三星正式开始采用其 SF3E(3nm 级、早期全栅)工艺技术大批量生产芯片,但没有无晶圆厂芯片设计商证实其产品使用了该节点。但 TechInsights 最近发现 ,比特微的 Whatsminer M56S++加密矿机使用的专用集成电路 (ASIC),确实是采用三星 SF3E 工艺制造的。

用于挖掘加密货币的 ASIC 往往是晶体管数量相对较少的小型设备,具有类似的重复逻辑结构和最少数量的 SRAM 位单元。这通常使得此类芯片,尤其是 Whatsminer M56S++,由于其生产简单性,非常适合用作最先进制造技术的pipe cleaners。对于 Samsung Foundry 来说,将其 SF3E 用于加密货币挖掘 ASIC 等芯片是非常有意义的。

不幸的是,我们对Whatsminer M56S++ ASIC了解不多,只知道基于该芯片的MictoBT矿机具有240-256 Th/s算力和22J/T能效。

此外,我们目前也尚不清楚三星的 SF3E 目前是否用于加密货币挖矿芯片以外的应用。但三星官方表示,它使用最新的工艺节点生产产品。

三星在之前发布财务报表中写道:“我们正在批量生产第一代 3 纳米工艺,产量稳定,并且基于这一经验,我们正在开发第二代工艺,以确保更大的批量生产能力。”

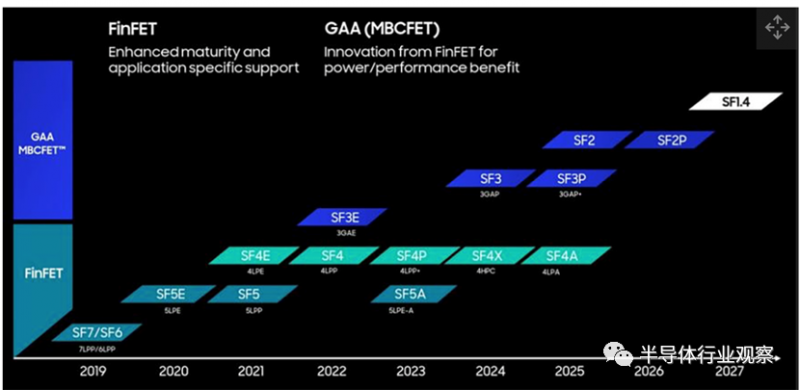

与三星第二代 5nm 级技术(SF5、5LPP)相比, SF3E (又名 3GAE)有望在保持相同复杂性和频率的同时将芯片功耗降低多达 45%,或者在类似的情况下将性能提高 23%。晶体管数量和时钟。此外,它还可以将集成电路(IC)占用的面积减少16%。该公司最近详细介绍了名为SF3的第二代 3nm 级工艺 。

三星3nm良率正在提升

目前,只有两家代工厂为其客户提供 3 纳米和 4 纳米级工艺技术:台积电和三星代工厂。但商业媒体有时会将前沿节点的良率归咎于三星代工,但这一点无法得到证实。但最近的一系列报告称,三星现在正在向商业客户交付首款基于 GAAFET 的 3 nm 芯片,并且三星 3 nm 和 4 nm 级节点的良率总体状况良好。

三星代工的4纳米级工艺技术良率现已高于75%。相比之下,据Kmib.co.kr报道,根据 DGB 金融集团成员 Hi Investment & Securities 的报告估计,SF3E(3nm 级、早期全栅)芯片的良率现已超过 60% 。同一份报告称,台积电 N4 节点的良率接近 80%,但同样,这是研究人员的估计。

一般来说,有关代工厂良率的信息无法得到验证,因为合同晶圆厂几乎从不公开谈论良率。他们有时会公开披露与以前的节点相比的缺陷密度,但三星代工的 SF4E、SF4、SF4P 和 SF3E 的情况却并非如此。

三星代工官方只表示其SF3E工艺技术已经量产,良率稳定(可能是为了回应去年年底有媒体报道SF在SF3E上良率不稳定的报道),下一代的工艺的开发正在进行中。

三星在一份声明中写道:“我们正在批量生产第一代 3nm 工艺,产量稳定,并且基于这一经验,我们正在开发第二代工艺,以确保更大的批量生产能力。”

基于上文提到的矿机芯片,我们能间接证实三星 5 纳米和 7 纳米级制造工艺的良率正在提高。据DigiTimes 报道 ,三星代工厂 5 纳米生产线的利用率已增至 80%,5 纳米和 7 纳米工厂的综合利用率近期已从 2022 年的 60% 攀升至 90%。再次强调,该信息来自非官方来源。

通常,无晶圆厂芯片设计人员不倾向于使用高缺陷密度的节点,因此如果5纳米级(三星的SF4源自SF5)的利用率变高,这可能表明它们现在被三星客户更密集地使用。或者,这可能表明三星代工厂的客户迫切希望提高产量,尽管由于需求高而导致产量较低。然而,考虑到当前的市场状况,情况可能并非如此。