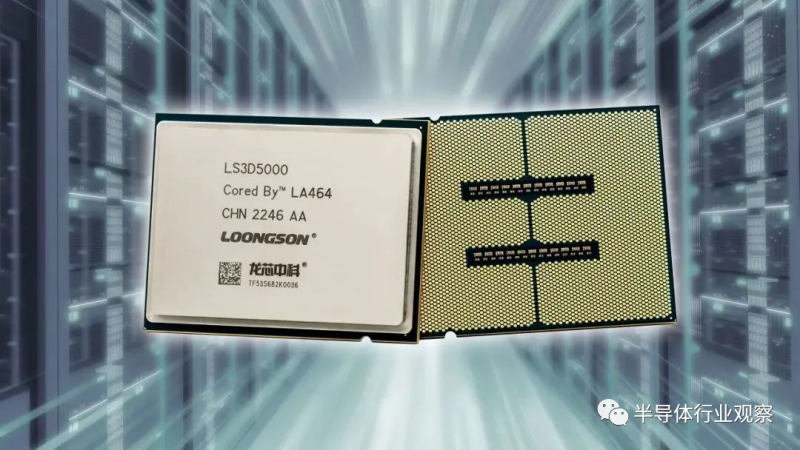

具体来说,3D5000芯片是使用Chiplet(芯片粒)技术把两块之前发布的3C5000芯片互联和封装在一起,其中每块3C5000芯片粒有16个核心,从而实现3D5000的32核设计。除了集成了32个LA464处理器核之外,龙芯3D5000还集成了64MB的L3 Cache,支持最多8个DDR4-3200 DRAM;在可扩展性方面,3D5000可以通过HyperTransport接口构建至多四路处理器,因此单机可以支持多达128核。

在性能方面,龙芯的这款芯片使用的是SMIC的12nm工艺,时钟频率可达2.2 GHz。跑分方面,单路和双路服务器的SPEC CPU2006 Base实测可以超过400分和800分,预计四路服务器的分值可以达到1600分。根据时钟频率和跑分结果来看,该芯片性能大约和Intel 2015年的至强CPU(Xeon E5-4620, 2.1GHz,四块芯片的SPEC CPU2006分数为1550)接近。

我们认为,龙芯的3D5000芯片对于国产自主产权处理器来说是一个重要的里程碑。其重要性不仅仅是由于它的性能在慢慢接近主流处理器水平(虽然还有一段距离),而且在于它使用了Chiplet技术。从芯片架构方面来看,龙芯还有相当的潜力可挖(对照的Intel Xeon E5-4620使用的是32nm工艺),处理器架构方面的技术也不是一朝一夕能解决的,而需要踏踏实实地积累技术——值得欣慰的是,龙芯已经宣布将于明年发布使用全新架构的处理器,其IPC(instruction per cycle,每时钟周期指令执行数,是CPU最重要的指标之一)可望能达到AMD Zen3水平。

另一方面,我们也看到使用12nm工艺确实对于该芯片的时钟频率给了很大的限制,在目前主流使用最先进半导体工艺的CPU时钟频率都在接近4GHz的时候,3D5000的时钟频率仅为其一半左右。但是,这也是3D5000芯片重要的原因,因为它使用了Chiplet技术,而Chiplet技术可望是能成为处理器(以及其他品类的芯片)突破半导体工艺限制瓶颈的最关键技术。

Chiplet给国产芯片的价值

如前所述,Chiplet将会成为国产芯片突围的重要技术。

目前由于地缘政治的影响,中国的半导体行业受到了种种限制,尤其是开发自主知识产权的关键芯片(如国产CPU,或者之后有可能受到影响的其他高性能计算芯片)的公司难以使用最先进的半导体工艺节点。另一方面,中国的半导体fab同样由于受到地缘政治的影响,难以快速追赶全球最先进的工艺节点,而目前只能主要生产成熟工艺节点(如28nm),或者是介于成熟工艺和先进工艺之间的工艺节点(例如SMIC今年刚开始大规模量产14nm,未来几年可望做到10nm以下)。即使是介于成熟工艺和先进工艺之间的工艺节点,也会存在良率较低等问题,需要时间来解决。

在这样的情况下,国产自主知识产权芯片在受到地缘政治影响下只能使用较落后的工艺节点,那么使用Chiplet这样的高级封装技术就成为了突破工艺限制,或者说至少减少工艺对于芯片影响的一种重要技术。

首先,从架构上来说,以CPU为例,当单核性能受到工艺的限制难以做到很强,时钟频率难以跑到很高的时候,使用多核就是一种重要的提高性能的选项。当在核心数量上做提升的时候,确保核心与核心之间的高性能数据互联就是一项重要的任务,而这项任务使用基于Chiplet的技术可以较为容易地实现,从而保证多核处理器的总性能能以和核心数量呈接近线性的方式提升。我们认为,这样的设计方式不仅仅对于CPU这样的处理器有效,而且对于其他高性能计算芯片,例如汽车芯片、GPU等等都有意义,因此龙芯的3D5000芯片对于整个行业都有很大的借鉴意义。我们认为,未来这种使用Chiplet方法的众核CPU很可能是国产CPU的主流做法,而龙芯这次发布的芯片将会是这方面的先驱者之一。

其次,从良率角度来看,如前所述国内的Fab由于良率可能会存在一定的提升空间,而良率又会影响到芯片的成本。为了国产芯片能有较低的成本可以在市场上有竞争力,必须保证总体良率足够好,而这个时候Chiplet就能提供帮助。具体的原因是,在使用同一工艺的前提下,总体芯片的良率和芯片的尺寸有关,即在单个芯片上集成越多晶体管,总体芯片尺寸越大,则芯片良率越低;如果工艺本身的良率就有提升空间,那么对于芯片尺寸较大的CPU或者高性能计算芯片,总体的芯片良率就会很低。为了解决这个问题,可行的做法是把一个大芯片拆成多个小的芯片粒,这样单个芯片粒的面积就会较小,从而良率得到了保证,从而整体上可以用高级封装的方法来实现在工艺良率还在提升的时候,也能实现较高良率的高集成度芯片。

中国芯片设计应布局Chiplet以及相关架构

值得一提的是,使用Chiplet并非是为了突破地缘政治对于中国半导体影响的临时解决方案,而事实上将会成为未来芯片设计的主流方案——即使没有地缘政治对于中国半导体技术的限制,中国半导体行业仍然应该大力发展Chiplet相关的技术。

目前,国际最主流和最领先的半导体芯片公司都在使用Chiplet技术,因为他们也受到了半导体工艺的限制,因为工艺良率的问题在最新的半导体工艺节点中也存在,因此AMD、Intel等顶尖公司都在大量投入Chiplet相关研发,并且已经使用在最新的芯片中,用以提高芯片性能和良率。因此,中国半导体公司对于Chiplet的研发事实上也是符合全球半导体主流技术的做法。

对于Chiplet技术来说,一方面必须在封装和相关半导体工艺上做投入——从目前的技术来看,Chiplet以及相关的高级封装技术正在越来越多地在半导体代工厂中完成(例如台积电的InFO、CoWoS、SOIC等都是相当成功的Chiplet相关技术),而不是在封测厂中完成,因此中国的半导体代工厂也必须要努力开发相关的技术。另外,从芯片设计端来看,Chiplet为芯片设计带来了更多的灵活度,开启了更多的机会,但是同时也对于芯片架构设计提出了更高的要求,即如何针对Chiplet去开发最优的芯片架构,从而最大程度上利用Chiplet带来的灵活度;例如目前AMD的最新一代处理器中把大量缓存放在了Chiplet中,这就是Chiplet给芯片架构带来的一次更新。因此,如何利用Chiplet的带来的机会让中国半导体芯片行业更上一层楼,是需要中国的相关的半导体工艺、封装和设计厂商协同努力的一个重要课题。