在行业中,我们看到越来越多的系统示例通过异构集成构建,利用 2.5D 或 3D 连接。在这次采访中,imec 高级研究员、研发副总裁兼 3D 系统集成项目总监 Eric Beyne 回顾了趋势并讨论了构建下一代 3D 片上系统所需的技术。各级报告的进展将使系统设计和开发进入下一个层次,有望在系统的功率-性能-面积-成本 (PPAC) 指标中获得巨大回报。

未来几年哪些主要趋势将标志着您的研究领域?

imec 正在探索哪些途径来克服未来的挑战?

还有其他值得一提的技术发展吗?

我们在实现背面供电网络方面取得了哪些进展?

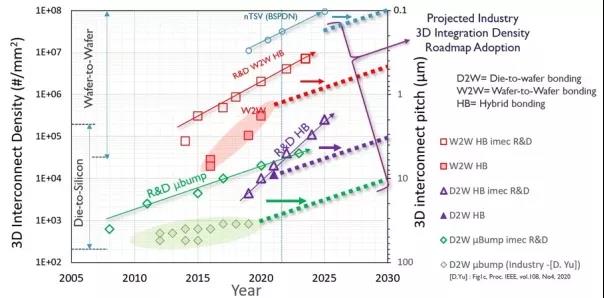

能否详细介绍一下imec的3D集成技术为行业带来的附加价值?

是什么让 imec 的 3D 系统集成计划在全球半导体行业中独一无二?