根据台湾媒体的最新消息,台积电1nm制程将落脚嘉义科学园区,台积电已向相关管理局提出100公顷用地需求,其中40公顷将先设立先进封装厂,后续的60公顷将作为1nm建厂用地。对于这一传闻,台积电表示,选择设厂地点有诸多考量因素,台积电以中国台湾地区作为主要基地,不排除任何可能性,也持续与管理局合作评估合适的半导体建厂用地。产业人士预估,台积电1nm的投资可能超过万亿新台币的级别。

1nm的技术难度极高,可能已经是极限

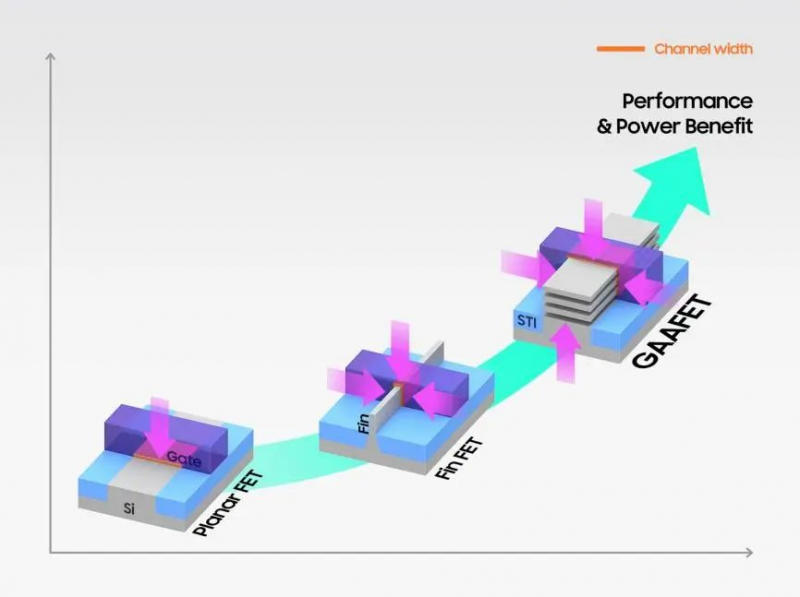

1nm被很多人定义为芯片制造工艺的极限,主要原因是,1nm确实已经逼近晶体管制造的物理极限,将会衍生出很多技术难题。当前,先进制程的主要工艺结构是FinFET (鳍式场效应晶体管) ,又称3D晶体管。FinFET使用Gate对Fin的包围实现等效W值的增加,可以更有效地控制沟道区域,进而更好地控制电流流动,减少漏电流,并能够有效抑制短沟道效应,提高了设备的性能和能效。FinFET结构由衬底上的硅体薄(垂直)翅片组成,栅级围绕通道提供了良好的通道三面控制。

从22nm芯片一直用到5nm,FinFET都是首选结构。不过,到了3nm工艺后,静态电流泄漏问题变得越来越严重——在3nm工艺里,FinFET对电流的控制能力急剧下降,同时漏电流也在升高。台积电计划在2nm工艺里开始使用第三代工艺结构——GAA-FET(环绕式栅极场效晶体管),三星在3nm工艺里已经开始使用这种结构。GAA-FET通过四面环绕 Channel,实现对Channel 更强的控制,进一步减小短沟效应的影响。

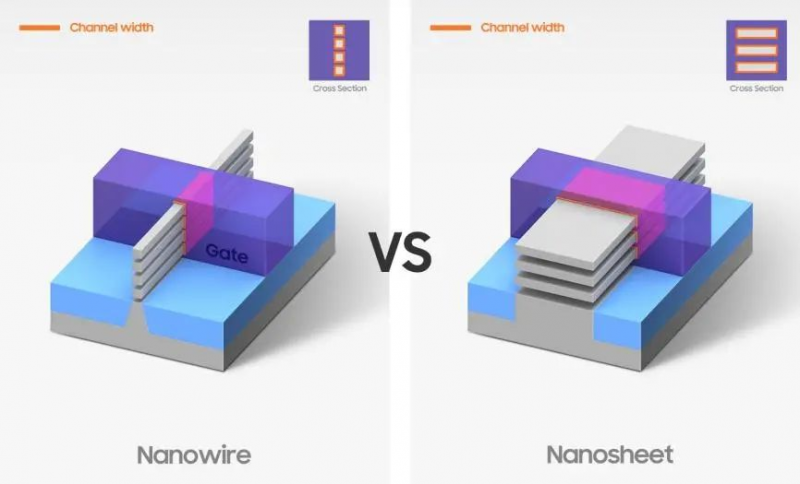

图源:三星半导体根据三星半导体的介绍,GAA结构有线型(Wire)和片型(Sheet)两种形态。Nanowire GAA 必须堆叠多层Wire以加宽总沟道宽度,这使得工艺变得更加复杂。为了解决这个问题,三星半导体没有选择线型(Wire),而是采取了宽度更宽的片型(Sheet)形态的GAA,也就是MBCFET。

图源:三星半导体根据台媒的报道,台积电也已经正式顺利实现GAA技术2nm制程。从工艺进度来说,2nm之后并不是马上迎来1nm,而是1.4nm,现在的叫法可能是14A,之后就是1nm。台积电此前透露,该公司已经于2022年开始组建1.4nm的团队,因此现在启动1nm研发也不意外。在1nm量产中,预计三星和台积电可能还会使用GAA-FET,不过可能会是GAA-FET的进一步演化版,IEDM会议上曾提到过,其中一个演化架构是Forksheet架构。

英特尔则认为,可以使用堆叠式CFET场效应管架构,这也是一种GAA-FET的改进结果,属于堆叠式的GAA-FET,将n型和p型MOS元件堆叠在一起。

不过即便是有结构改进,1nm还是需要面临很多挑战,比如更加突出的量子隧穿现象。该现象指出,当芯片制造工艺来到1nm时,电子会发生量子隧穿现象,这会导致晶体管的性能受到限制。量子隧穿实际上就是不受控制的漏电,造成不可控的发热。

为了让漏电可控,材料创新和结构创新一样重要,为了实现1nm制程,业界很早就开始研发新材料以应对新挑战。目前产业界已经证明,使用非硅材料可以实现1nm制程。2019年,IMEC就提出,2D材料可实现1nm以下的工艺节点。当时所采用的材料是二硫化钼(MoS2) 。

二硫化钼一个重要的特性是可以以稳定的形式生长,厚度仅为一个原子,且在该尺度上具有原子精度。台积电同样在进行2D材料的探索,台积电和麻省理工学院、南洋理工大学曾联合发表了一篇论文,描述单层材料如何受到金属导电间隙的影响。论文指出,通过使用金属铋和一些半导体单层过渡金属二硫族化物,可以实现更小的晶体管,这些2D材料包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)。很多业者认为,1nm量产面临多方面的问题,很可能已经是芯片制造工艺的极限。

1nm芯片非常昂贵,光刻机就超过4亿美元

除了技术和材料方面的挑战之外,晶圆代工厂想要量产1nm,也需要承担成本和客户方面的风险,因为1nm工艺确实是太贵了。有分析报告指出,想要制造1nm芯片,现有的光刻机都不能满足需求。全球光刻机龙头企业ASML预计,将会在2025年,也就是2nm量产之后再更新一代光刻机,基于High NA技术,将NA指标从当前的0.33提升到0.55,进一步提升光刻分辨率。

这个下一代光刻机将主要用于1.4nm工艺的量产,售价是非常昂贵的,将达到4亿美元,是现有光刻机价格的2.8倍。然而,这可能还不是极限。ASML表示,这款0.55NA数值孔径的EUV光刻机应该能够支撑至少1.4纳米芯片的制造,但对于1纳米芯片而言,目前尚无确切明确的方案。

那么,我们也可以理解为,如果再需要给1nm重新设计光刻机,价格可能会更高。然而,就现在这个1.5亿美元的光刻机,以及工艺成本,已经让台积电有点吃不消了。回看台积电从2022年第四季度到2023年第二季度的毛利率,从62.2%下降到了54.1%。就这样,也就只有苹果公司用得起。

据悉,台积电3nm工艺每片晶圆的价格大概是2万美元,5nm时是1.6万美元。台媒指出,苹果作为唯一的3nm用户,拥有很强的议价能力,将3nm成本压到一个很低的水平,进而导致台积电毛利率承压。而反观高通,本来可以借助3nm进一步拉近和苹果A系列的性能差距,不过由于价格太高,最终选择了三星的工艺。

3nm都是如此了,很难想象,下面要经过2nm、1.4nm之后才能到1nm,届时1nm的成本会达到一个怎样的程度。虽然1nm可能面临无人用得起的情况,不过产业界对于量产1nm依然是趋之若鹜。先不说已经展开军备竞赛的台积电和三星,英特尔对量产1nm也是信心满满,和台积电一样,甚至是比台积电更早,英特尔也有自己的1万亿个晶体管的芯片封装路线,在这个路线下,也包含1nm制造工艺。根据此前的报道,日本芯片制造商Rapidus与东京大学联手法国半导体研究机构Leti,也在共同开发1nm芯片。

另外,IBM和IMEC也在致力于量产1nm。当然,也有人质疑1nm的存在合理性。根据预期数据,1nm芯片相比于现有的5nm芯片,其性能可能提升20%至30%,而功耗可能降低25%至40%。不到50%的能效提升,却需要为此支付数倍,甚至是数十倍的成本,终端市场可能很难接受这样的芯片。

不过,赞同的人认为,1nm可能会通过材料创新等开启芯片制造的新模式,我们无法用今天的眼光去定义未来的科技创新,就像我们当年从微米时代进入纳米时代,以及40nm进入28nm一样,1nm技术的高成本和复杂性也可能导致半导体行业的进一步集中,但同时也会出现更新的高性能运算应用来启用1nm工艺。

摩尔定律是一个经济定律,虽然放缓了,不过还远远没有到消亡的时刻。按照台积电等厂商的计划,预计将会在2026年量产1.4nm工艺,然后在2028年1nm将正式量产。不过,从目前的情况来看,延期是大概率事件。1nm已经突破了硅材料的极限,因此除了需要更先进的光刻机等设备之外,材料创新也是一大重点,在此过程中,产业界可能会摸索到一条崭新的工艺迭代路径,将先进工艺水平继续向下推进。站在现在的节点说,1nm太贵完全没有必要,还为时过早。