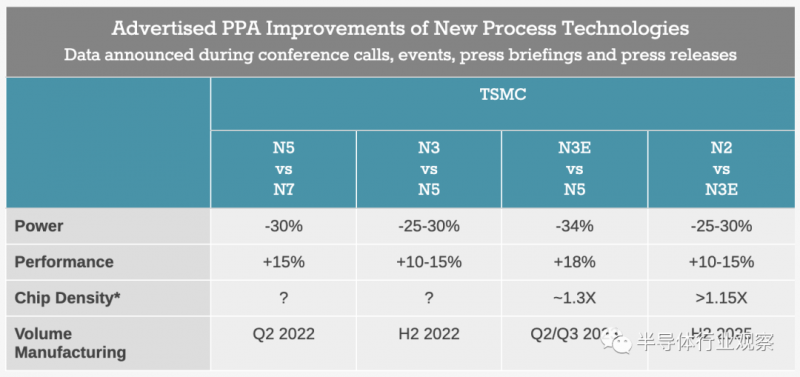

台积电上周在欧洲年度开放创新平台论坛上向合作伙伴发表讲话时表示,台积电路演的很大一部分致力于该公司的下一代代工技术。台积电的 2 纳米级 N2、N2P 和 N2X 工艺技术 将引入多项创新,包括纳米片环栅 (GAA) 晶体管、背面功率传输和超高性能金属-绝缘体-金属 (SHPMIM:super-high-performance metal-insulator-metal)未来几年的电容器。

但台积电警告说,为了利用这些创新,芯片设计人员将需要使用全新的电子设计自动化 (EDA)、模拟和验证工具以及 IP。虽然做出如此大的转变从来都不是一件容易的事,但台积电很早就给芯片设计人员带来了一些好消息:即使 N2 还需要几年时间,许多主要的 EDA 工具、验证工具、基础 IP 和甚至 N2 的模拟 IP 也已可供使用。

台积电设计基础设施管理主管 Dan Kochpatcharin 在阿姆斯特丹举行的 OIP 2023 会议上表示:“对于 N2,我们可以提前两年与他们合作,因为 Nanosheet 是不同的。” “[EDA] 工具必须准备就绪,因此 OIP 所做的就是尽早与它们合作。我们拥有一支庞大的工程团队来与 EDA 合作伙伴、IP 合作伙伴和[以及其他]合作伙伴合作。”

原定于 2025 年下半年某个时间开始生产 N2 芯片的准备工作很早就开始了。Nanosheet GAA 晶体管的行为与熟悉的 FinFET 不同,因此 EDA 和其他工具和 IP 制造商必须从头开始构建他们的产品。这就是台积电开放创新平台(OIP)展示其实力的地方,使台积电的合作伙伴能够提前开始开发他们的产品。

目前,Cadence、Synopsys等主流EDA工具,以及Ansys、西门子等多家EDA工具均已通过台积电认证,芯片开发者已经可以使用这些工具进行芯片设计。此外,Cadence 和 Synopsys 的 EDA 软件程序已准备好进行模拟设计迁移。此外,Cadence 的 EDA 工具已经支持 N2P 的背面供电网络。

对于预构建的 IP 设计,事情会花费更长的时间。TSMC 的基础库和 IP,包括标准单元、GPIO/ESD、PLL、SRAM 和 ROM,已准备好用于移动和高性能计算应用。同时,一些 PLL 存在于硅前开发套件中,而其他 PLL 则经过硅验证。最后,非易失性存储器、接口 IP 甚至小芯片 IP 等模块尚不可用——这成为一些芯片设计的瓶颈——但这些模块正在由 Alphawave、Cadence、Credo、eMemory、GUC 等公司积极开发或计划开发,根据台积电的幻灯片,新思科技(Synopsys)。最终,用于设计 2 nm 芯片的工具和库生态系统正在整合,但尚未全部实现。

“[开发具有纳米片晶体管的 IP]并不难,但它确实需要更多的周期时间,周期时间有点长,”Kochpatcharin 说。“其中一些 IP 供应商还需要接受培训,[因为]它们只是不同。从平面 [晶体管] 到 FinFET,并不难,你只需要知道如何制作 FinFET。[这是]同样的事情,你只需要知道如何做[这个]。所以,确实需要一些时间来接受培训,但是[当你接受培训时],这很容易。所以这就是我们早开始的原因。”

尽管芯片的许多主要构建模块都已支持 N2,但在台积电的 2 纳米级制程技术投入量产之前,许多公司仍需完成大量工作。倾向于自行设计(或共同设计)IP 和开发工具的大公司已经在开发 2 nm 芯片,并且应该在 2025 年 2 月开始量产时准备好产品。其他玩家也可以火起来他们的设计引擎,因为台积电及其合作伙伴正在顺利进行 2 纳米准备工作。

下一代芯片需要合作

今年,台积电将庆祝其开放创新平台成立 15 周年,这是一项多方面的计划,将代工厂的供应商、合作伙伴和客户聚集在一起,帮助台积电的客户高效、及时地更好地构建创新芯片。OIP 计划多年来不断发展,目前涉及数十家公司和超过 70,000 个适用于各种应用的 IP 解决方案。它持续增长,当下一代技术(例如 2 nm)和先进封装方法在未来几年成为主流时,其重要性将比以往任何时候都更高。

台积电设计基础设施管理主管 Dan Kochpatcharin 在荷兰阿姆斯特丹举行的 OIP 2023 会议上表示:“这不是一个营销计划,它实际上是一个为行业提供支持的工程计划。” “我们拥有一支庞大的工程团队来与 EDA 合作伙伴、IP 合作伙伴和设计合作伙伴合作。”

加快上市时间是台积电 OIP 计划的基石之一。在2008年OIP计划出现之前,台积电将在大约18个月的时间内开发出工艺技术和工艺开发套件(PDK),然后将PDK和设计规则移交给其电子设计自动化(EDA)软件和IP开发商中的合作伙伴。后者将再花费 12 个月创建 EDA 工具并构建 IP 模块,然后向实际芯片设计人员提供程序和 IP 解决方案。然后,芯片开发商还需要 12 个月的时间来构建实际的芯片。

借助 OIP,台积电的 EDA 工具和 IP 设计合作伙伴可以在台积电开始开发其新生产节点几个月后开始开发其产品。而且,代工厂声称,当台积电最终确定其工艺技术时,EDA 工具和 IP 已经为芯片设计人员准备好了。台积电表示,这将产品上市时间缩短了约 15 个月。与此同时,随着新节点的开发时间和芯片的开发时间越来越长,台积电与 EDA 和 IP 提供商之间早期合作的价值正在增加。

例如,台积电两年来一直在与合作伙伴进行 N2(2 纳米级)EDA 和 IP 准备工作,台积电的目标是在 2025 年下半年为芯片设计人员准备好工具和通用 IP。

热心的读者可能会想知道,为什么即使该计划取得了成功,OIP 在 15 年内只增长到 39 个 IP 成员。Dan Kochpatcharin 表示,事实证明,台积电对加入该计划的公司极为挑剔。台积电需要 OIP 计划的成员真正为其做出贡献,并使共同努力大于所有部分的总和。由于台积电客户使用 OIP 计划参与者提供的 IP、软件和服务,因此后者必须在其领域非常出色才能成为 OIP 的一部分。

事实上,台积电甚至有其 TSMC9000 计划(名称模仿 ISO 9000 质量政策),为 IP 设计设定质量要求。IP 合作者接受 TSMC9000 评估,结果可在 TSMC-Online 上获取,为客户提供有关 IP 可靠性和风险的指导。

“我们对 IP 进行了大量的资格认证,在 test shuttles进行流片之前,他们有 TSMC 9000 检查表,[...]客户可以在 TSMC-Online 上看到[所有]结果,”Kochpatcharin 解释道。“所以,他们可以看到,这个 IP 得到了硅片的引入,因此,他们对该 IP 更有信心。[他们还看到]有多少客户采用了 [这个 IP]、有多少流片以及有多少产品。对于缺乏更好的术语,即知识产权消费者报告。”

联盟成员在台积电的首要目录中列出了他们的 IP,其中包含来自 39 个贡献者的数千个 IP 选项。客户可以使用台积电在线设计门户上的“IP中心”搜索IP。目录中的每个 IP 均由其原始合作伙伴开发、销售和支持。同时,芯片开发人员甚至可以查看一个IP或另一个IP的受欢迎程度,这可以让芯片开发人员对他们的选择更有信心。如今,信心非常重要,而且对于 3 纳米、2 纳米以及未来的节点来说,随着流片变得更加昂贵,信心将变得更加重要。

但加快上市时间和确保质量并不是 OIP 计划的唯一目的。它旨在简化芯片的开发、生产、测试和封装。台积电的 OIP 涉及多种成员,并分为六个计划或联盟,每个计划或联盟负责不同的工作:

一、IP 联盟专注于提供经过硅验证、生产验证和代工厂特定的知识产权 (IP),供台积电客户选择。

二、EDA 联盟包括提供符合台积电技术要求并支持代工厂生产节点的电子设计自动化 (EDA) 软件的公司。

三、设计中心联盟由合约芯片设计师以及提供系统级设计解决方案支持的公司组成。

四、云联盟结合了 EDA 工具制造商和云服务提供商,使台积电的客户能够在云中开发和模拟他们的芯片,以减少内部计算需求。

五、3D Fabric Alliance 联合了所有负责先进封装和多芯片处理器开发的公司,主要包括上述所有公司以及存储器制造商(包括美光、三星和 SK Hynix)、基板、OSAT、和测试设备制造商。

六、价值链联盟类似于设计中心联盟,但旨在提供更广泛的合同芯片设计服务和 IP 产品,以满足从初创公司、OEM 到 ASIC 设计人员等广泛客户的需求。

3D Fabric Alliance计划于去年年底推出,因此可以被认为是OIP的最新成员。与此同时,3DFabric 联盟希望通过新成员快速扩张,这是有原因的。

工艺技术变得越来越复杂,这一点不会改变。随着 Ansys、Cadence、Siemens EDA 和 Synopsys 等 EDA 制造商将人工智能功能融入到他们的工具中,芯片设计工作流程可能会变得更加容易。但由于高数值孔径 EUV 光刻扫描仪将掩模版尺寸从 858 mm2减半至 429 mm2,看来大多数人工智能和高性能计算 (HPC) 处理器将在未来几年采用多块设计,这将推动对有助于创建多块解决方案、先进封装、HBM 型存储器和全新测试方法的软件的需求。这将再次增加全行业合作的重要性以及台积电OIP的重要性。

“[我们自 2016 年以来一直提供 InFO_PoP] 和 InFO_oS 3D IC,[3D IC 已经]投入生产多年,[但]当时它仍然是一个利基[市场],”Kochpatcharin 说。“客户必须知道他们在做什么 [...],而 [当时] 只有少数人可以制作 3D IC。[2021 年],我们推出了 3DFabric 活动,我们希望使其对所有人通用,因为有了人工智能和[来自多家公司]的 HPC,[这些] 不再是小众事物。因此,每个人都必须能够使用 3D IC。[例如],汽车是 3D IC 的一个精彩[应用],有一个[巨大的市场]。] 市场在那里。”

与此同时,为了实现芯片之间和小芯片之间的下一代连接,台积电预计将需要硅光子学,因此该公司正在其 OIP 计划中积极朝这个方向努力。

“如果你进入 N2,下一个出现的就是硅光子学,”Kochpatcharin 说。“我们在这里启动了一个流程,需要 [设计服务合作伙伴] 才能为客户提供支持。”