目前,以5G、AI和汽车所带来的数字化趋势正将半导体市场推向新高。对广大半导体行业企业而言,如何在数字化芯片设计与制造大潮来临之际,迎头赶上并占据优势地位方面,正面临着新的挑战和机遇,而在推动半导体技术带来变革的数十年里,EDA软件是提升半导体设计生产力的基础工具。

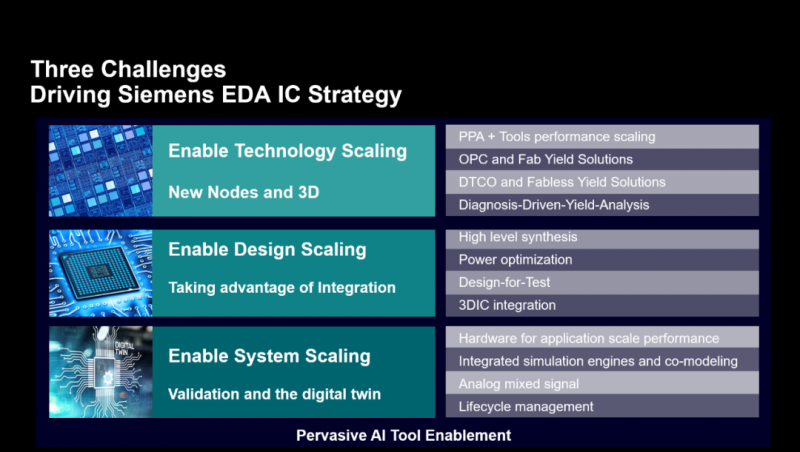

2022年12月27日,在中国集成电路设计业2022年会(ICCAD)上,西门子EDA中国区产品总监牛风举先生发表了《西门子EDA——AI、5G&汽车芯片解决方案》的演讲,介绍了为应对5G、AI和汽车领域对芯片提出的新需求,西门子EDA从芯片制造技术演进、芯片设计规模演进和片上系统复杂度演进三个方面进行的技术支撑和赋能。

先进工艺技术演进

过去几十年来,半导体行业遵循摩尔定律不断向前发展,目前从行业的进度上来看,先进制程技术将继续演进,新的工艺节点和3DIC技术将继续支撑芯片的不断微缩,3nm是行业正在突破的工艺节点。另外,行业也正在探索新的方法进一步缩小芯片的尺寸。

但是随着工艺节点进入3nm及以下,芯片的设计复杂度和生产流程步骤不断增加,芯片的初始良率大幅下降,甚至不到50%,良率成为PPA挑战以外的一大新的挑战。对此,西门子EDA认为,需要从设计、测试和生产各环节对良率进行把控。值得一提的是,如果能采用DFT的诊断驱动良率分析技术(Diagnosis-Driven-Yield-Analysis),将会缩短85%的PFA循环时间。测试诊断正在驱动良率的分析,这也是目前行业正在采用的做法之一,前十大半导体中至少有7家在依赖诊断驱动良率分析技术(DDYA)来提高良率。

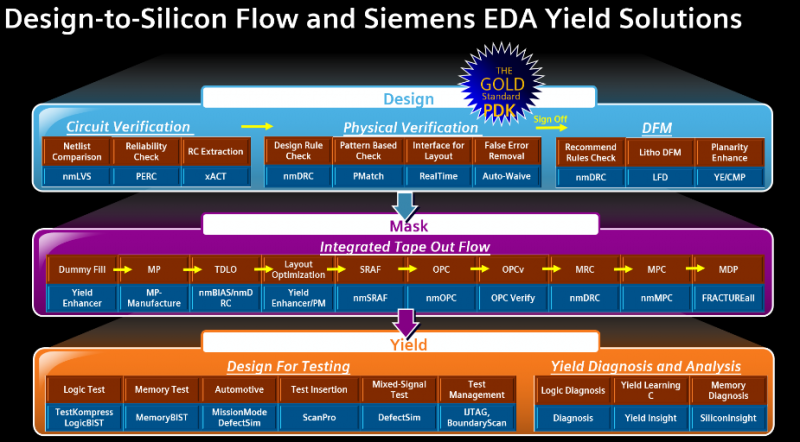

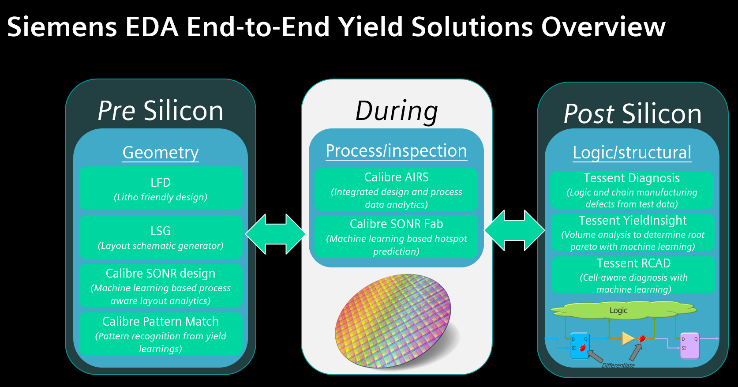

据西门子EDA中国区产品总监牛风举的介绍,西门子EDA的Calibre平台在提升良率方面有着卓越的成绩。Calibre物理验证平台涵盖了Signoff级验证的Design、Mask以及芯片制造过程中所有验证步骤。Calibre的诸多产品可以帮助客户实现端到端的良率问题把控,Calibre SONR 可以基于机器学习的工艺感知版图的分析来主动预防Pattern故障。

此外,Solido Variation Designer作为业界广泛认可的Variation-Aware良率验证解决方案,可以帮助客户提高IP设计鲁棒性,实现更加精准的路径延迟分析,高效解决复杂蒙特卡洛分析带来的设计挑战。Tessent Diagnosis的版图感知和标准单元感知技术,结合Tessent YieldInsight的无监督机器学习技术,可以找到最可能的缺陷分布并移除低概率怀疑点,从而提高分辨率和准确性。

如下图所示,西门子EDA通过在硅前、硅中和后硅三个阶段进行层层良率把关,进而提升先进制程的良率。

芯片设计规模的演进

面对芯片设计规模越来越大,西门子EDA工具需要从电路的高阶综合、功耗优化、测试成本压缩以及3DIC异构集成等方面进行全方位的技术支撑。

随着芯片设计验证复杂性的增加以及上市时间的压力,RTL的验证及重用成本也在增加,为了简化并加快整个设计、验证流程,工程师们开始寻求在更高的抽象层级上进行设计。对此,西门子EDA推出的Catapult HLS是业界唯一横跨ASIC、FPGA平台的C++ HLS工具,利用设计检查、代码和功能覆盖以及形式验证,减少多达80%的验证时间和成本。Catapult HLS还整合RTL代码功耗分析与优化工具PowerPro,为芯片设计公司提供了低功耗设计优化手段。目前Catapult HLS已经帮助诺基亚快速部署5G设备到多个国家。

西门子EDA的mPower电源完整性解决方案能为模拟、数字和混合信号IC设计提供可扩展的IC电源完整性验证。Esperanto公司表示,“在使用mPower之前,我们无法在1000 多个64位RISC-V的AI 芯片中一次性进行全芯片的EM/IR 分析,mPower帮我们获得了这种能力。”

测试成本压缩产生的经济效益随着芯片设计规模增大与日俱增,西门子EDA公司的Tessent Testkompress软件在2001年面世,至今每年为整个半导体行业的测试成本节约上百亿的美金。相较于传统的非压缩扫描链测试,目前TestKompress结合VersaPoint和SSN等新技术已经可以提供高达上千倍的测试压缩效果。

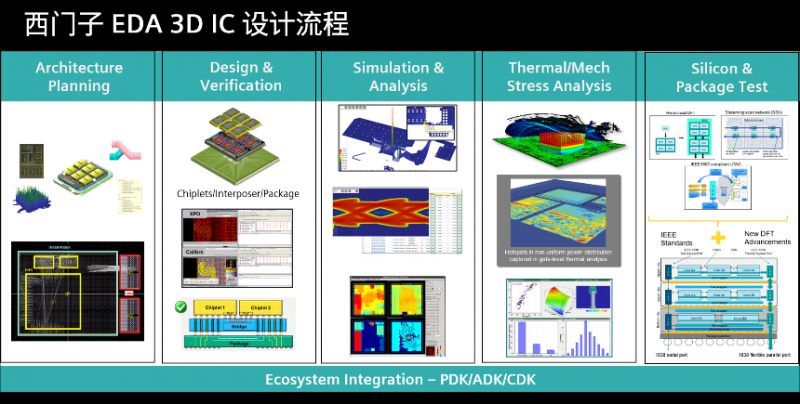

无疑,3D堆叠技术正成为应对芯片规模越来越大的一大重要手段。通过以最低成本实现最高水平的硅集成和面积效率,3D堆叠技术的重要性正在提高。在支持3D IC设计方面,西门子EDA有一套成熟的端到端的EDA解决方案,结合其Xpedition, Hyperlynx和Calibre,Tessent技术,实现了快速有效的设计至GDS 签核。例如,在芯片仿真验证阶段,结合西门子HyperLynx和Calibre系列工具,可以处理die、package和PCB仿真的协同问题,而不再是专注于单一设计领域;在测试阶段西门子EDA 推出了Tessent Multidie产品,为3D IC提供集成并且流畅的自动化EDA解决方案,通过灵活而完备的测试组合,实现提高测试覆盖率、降低测试成本、追踪良率问题等目标。

片上系统复杂度演进

现在汽车行业正在迈向“新四化”,牛风举表示,从传统汽车到下一代汽车的设计变迁中,发生了翻天覆地的变化:从传统的只需要大量的ECU逐渐过渡到少量域控制器、百米量级的导线长度转变为5G+芯片内的纳米级导线、由毫秒级延迟变成皮秒(picosecond)级延迟、瓦量级的功耗降为微瓦量级的功耗。除此之外,相比消费类的芯片车载计算机需要大算力和严格的安全功能验证。

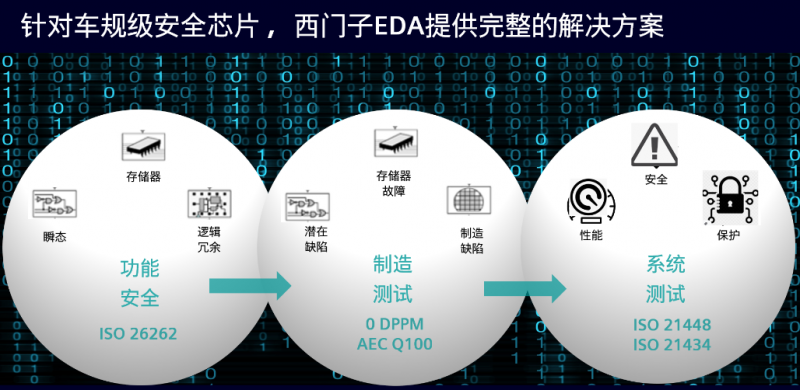

牛风举表示,从计算机的核心芯片CPU到手机的核心5G芯片,计算能力和通信能力被集成到一颗芯片,车载类脑芯片的集成复杂度会进一步演进,计算能力、通信能力和控制能力在不远的将来会被集成到一颗芯片,因此,电子/电气和机械协同设计是汽车数字化转型时代的新趋势。在这一形势下,考验的是EDA厂商从芯片设计过渡到整体机电一体化系统方案的设计。针对车规级安全芯片,西门子EDA提供了功能安全、制造测试、系统测试端到端的完整的汽车芯片解决方案。

西门子EDA在汽车芯片功能安全领域的具体解决方案主要有:

-

Austemper Design Systems可以从安全分析、安全设计、安全验证三个方面对汽车芯片的功能安全保驾护航。

-

OneSpin基于形式化引擎的FMEDA自动化方案是一套全面、统一的IC安全架构验证和核查流程,能快速计算安全机制的诊断覆盖率和其他ISO 26262指标,极大减少对故障仿真的需求。

西门子EDA在汽车芯片制造测试领域的具体解决方案主要有:

-

Calibre全线产品都通过了ISO26262的资格认证,确保汽车芯片能够被安全制造。

-

Tessent MissionMode方案可以进行在系统测试,其不仅支持上电自检、断电自检,还可以定期在线测试;

-

Tessent车规级芯片自动测试向量生成 (ATPG)解决方案可助力实现0 DPPM的目标,目前25%的IC供应商在生产中采用,且这一比例还在持续增长。

西门子EDA在汽车芯片系统测试领域的具体解决方案主要有:

-

Tessent UltraSoC提供结构化的监控能力,可以对制造和功能方面的缺陷进行防护,同时还可以防护黑客攻击等。

-

西门子EDA的PAVE360涵盖了汽车软、硬件子系统、整车模型、传感器数据融合、交通流量等场景,覆盖智能城市的仿真环境,以数字孪生为核心为下一代汽车芯片的研发,提供跨汽车生态系统、多供应商协作的综合环境;

结语

AI、5G和汽车所带来的数字化浪潮已经无法抵挡,牢牢把握这一发展趋势,西门子正在全速挺进,从芯片的底层构建创新的EDA底座,助力芯片这一数字化进程。