在7月27日凌晨举办的Intel Accelerated活动中,英特尔放出了几个重磅消息,未来制程节点的全面改名,后续先进制程的技术推进和时间节点,以及全新的封装技术和代工客户。

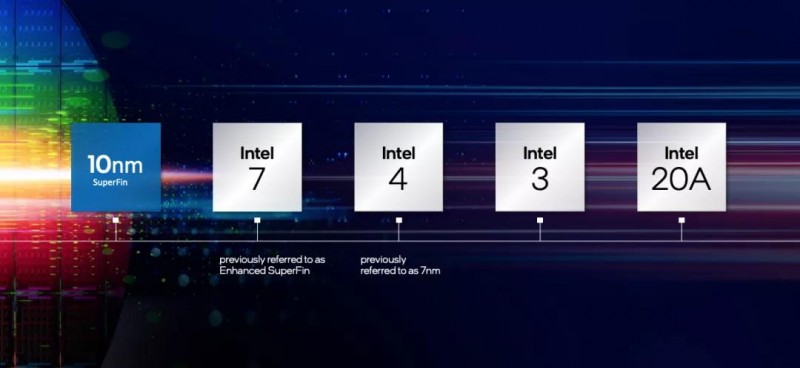

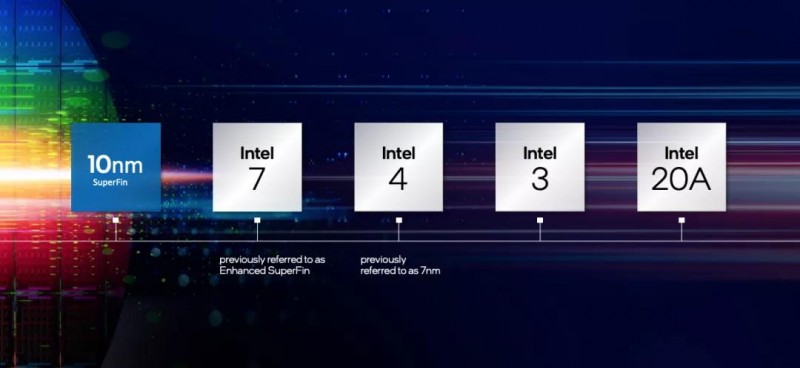

制程命名变更 / Intel

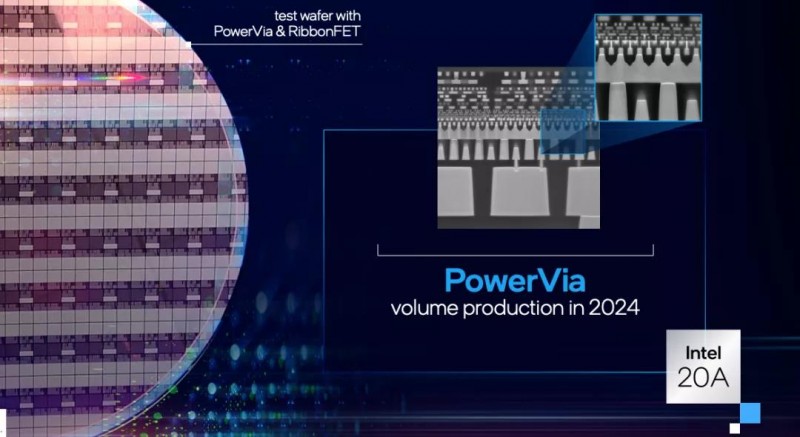

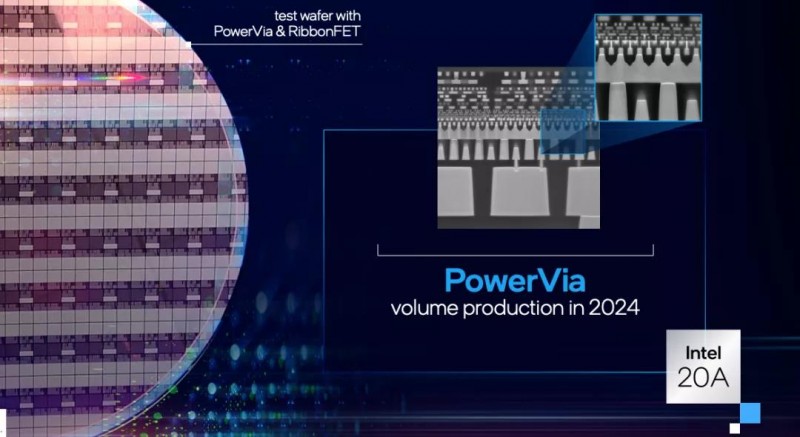

PowerVia技术与试产晶圆 / Intel

高通CEO寄语 / Intel

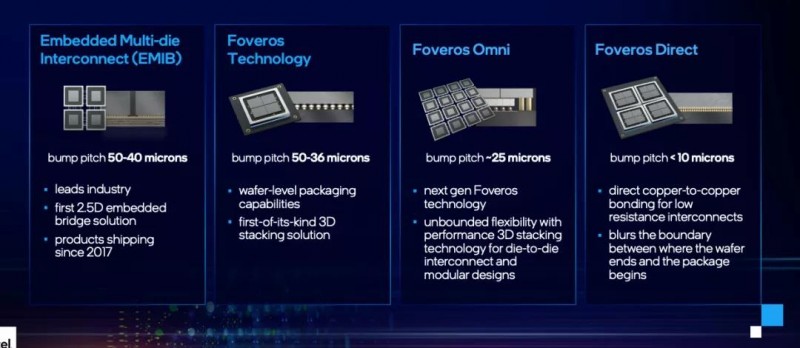

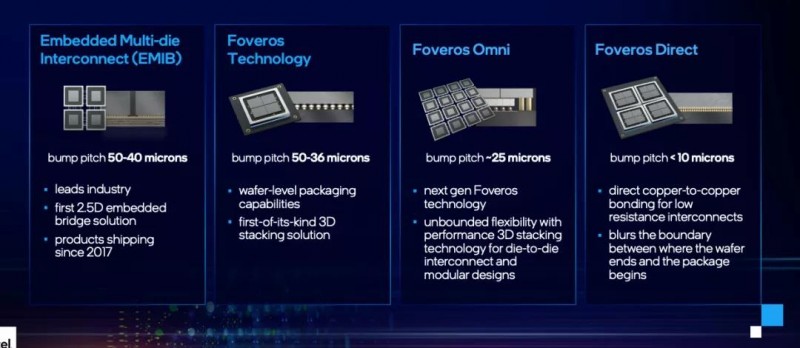

EMIB和Foveros / Intel

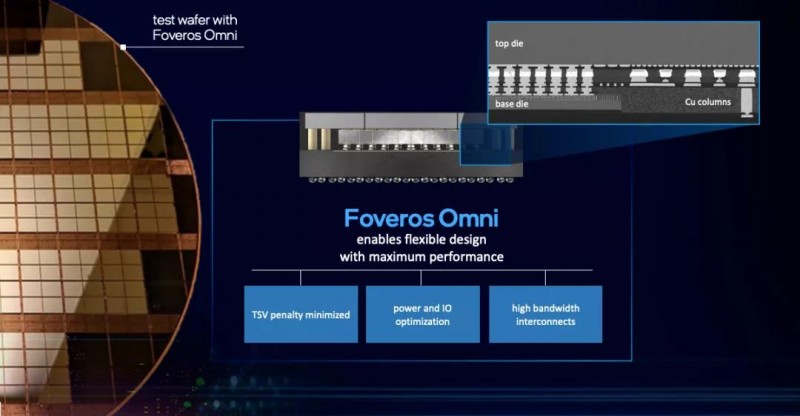

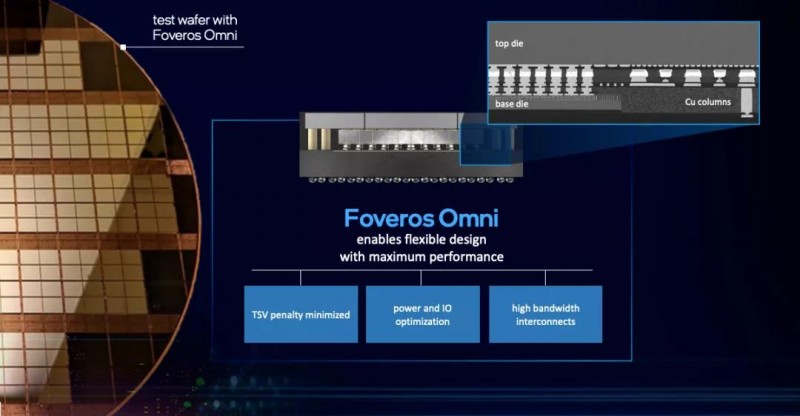

Foveros Omni与试产晶圆 / Intel

上一篇:国内一动力电池公司在美国上市

本文仅代表作者个人观点,与中自网无关。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容!来源网络如有误有侵权则删。