在半导体制造中,3nm工艺是继5nm MOSFET技术之后的下一个工艺节点。全球晶圆制造三巨头(英特尔、三星和台积电)都于2019年宣布了3 nm研发和量产计划。三星的3nm工艺率先采用GAAFET(栅极全绕型场效应晶体管)技术,他们自称为MBCFET(多桥沟道场效应晶体管);而台积电的3nm工艺仍继续使用增强的FinFET(鳍式场效应晶体管)技术,2nm工艺将转向GAAFET结构;英特尔有望于2023年发布基于GAA结构的5nm工艺(性能相当于前两家的3nm工艺)。此外,IBM最近发布的2nm工艺芯片一直就采用跟其7nm和5nm芯片一样的纳米片(nanosheet)结构,也就是业界通称的GAA技术。

3nm工艺竞赛

“3nm”这一术语已经与晶体管的任何实际物理尺寸(诸如栅极长度、金属间距或栅极间距)无关了。它已经成为半导体制造行业使用的一个商业或营销术语,指的是比前代(5nm及之前的工艺)芯片在晶体管密度、运行速度和功耗方面都更为先进的新一代硅半导体制造工艺。例如,台积电宣称,与之前的5nm相比,其3nm FinFET芯片在相同的速度下可将功耗降低25%至30%,相同的功耗前提下可将速度提高10%至15%,并将晶体管密度提高约33%。

下面我们简要回顾一下3nm工艺的研发和商业化进程:

-

2016年底,台积电宣布计划建设一个5 nm至3 nm节点晶圆制造厂,承诺投资额约为157亿美元。

-

2017年,台积电宣布在台湾台南科学园开始建设3纳米半导体制造厂,计划在2023年开始量产3 nm工艺芯片。

-

2018年初,IMEC和Cadence宣布使用极紫外光刻(EUV)和193 nm浸没光刻技术成功流片3 nm测试芯片。

-

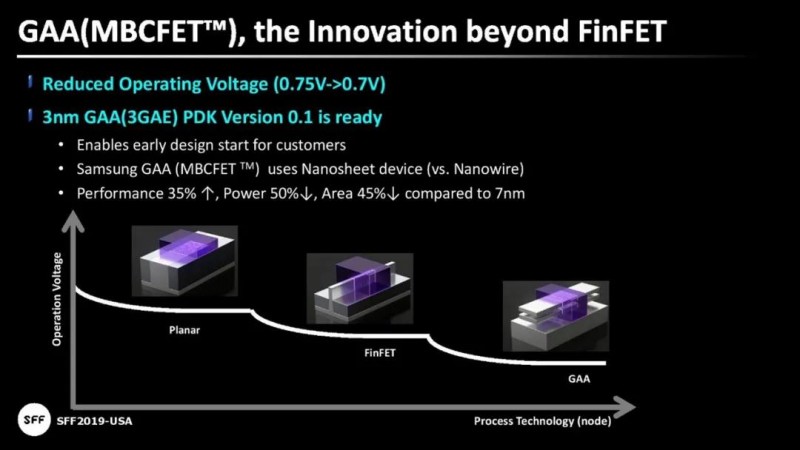

2019年初,三星提出计划在2021年使用其自研的纳米片(不是纳米线nanowire)MBCFET晶体管结构技术制造3 nm芯片。与7nm相比,这种芯片性能可提高35%,功耗降低50%,面积减少45%。

-

2019年12月,英特尔宣布于2025年量产3纳米芯片的计划,以及2029年生产1.4 nm的规划。

-

2020年1月,三星宣布开发出世界上第一个3纳米GAAFET工艺原型,并宣称将在2021年实现量产。

-

2020年8月,台积电发布其N3 3 nm工艺的细节。这是一种有重大改进的新工艺,而不是对N5 5 nm工艺的迭代升级。与N5相比,N3可将性能提高10–15%,或将功耗降低25–35%,逻辑密度增至1.7倍。台积电计划在2021年进行风险生产,并在2022年下半年实现量产。

-

2021年5月,IBM宣布研发出2 nm芯片制造技术,并成功制造出“指甲大小”的芯片原型,其晶体管数量超过500亿个。

台积电:2 nm转向GAAFET,与大学联合探索新材料“半金属Bi”

2018年末,台积电董事长刘德音预测芯片工艺将继续扩展到3 nm和2 nm节点,然而其他半导体专家尚不确定3 nm以下的节点是否可行。台积电于2019年开始研究2 nm,2020年8月在新竹建立2 nm技术研发实验室,预计今年将投入运营。在台积电从3nm迁移到2nm时,也将从FinFET转向GAAFET晶体管结构。据报道,台积电有望在2023年或2024年进入2 nm风险生产。

台积电的3nm, 2nm及至1nm工艺规划,目前将0.1nm视为“未来计划”,技术路线尚不明确。(来源:TSMC)

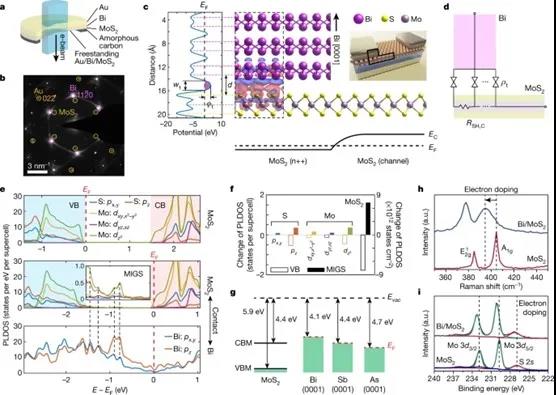

近日台湾和大陆媒体将台积电与台湾大学和MIT联合研发的新型半导体材料“半金属Bi“夸大为”1nm重大突破“,似乎压过了IBM本月初发布的2nm芯片。为证实这种“半金属Bi“的特性与未来潜力,ASPENCORE《电子工程专辑》分析师专门研读了5月12日在《自然》科学杂志上刊发的一篇题为《半金属与单分子层半导体间超低接触电阻》(《Ultralow contact resistance between semimetal and monolayer semiconductors》)文章。

据悉,这一创新的科研成果是由TSMC与国立台湾大学和MIT共同研发出来的。在芯片工艺不断发展的过程中,更低的通流电阻,和更小的导通损耗一直是业界研究的重点,而金属和半导体界面处的势垒,从根本上决定了接触电阻和电流传输能力,这也是制约二维半导体性能提升的关键。

单分子层 MoS2场效应管的欧姆接触和肖特基接触比较(图源:Nature)

此项研究成果表明,半金属铋Bi与单分子层二卤代烃(TMDs)半导体材料间的欧姆接触,其中金属感应间隙态(MIGS)被充分抑制,TMDs中的简并态在与铋接触时自发形成。通过这种方法,研究人员在单层二硫化钼(MoS2)上实现了零肖特基势垒高度、123Ω/um的接触电阻和1135uA/um的通态电流密度(这两个值分别是有记录以来的最低值和最高值)。

欧姆接触的原理和晶体结构(图源:Nature)

并且该研究团队在理论计算和试验验证方面均取得突破性进展,在TSMC成功制造出采用Bi-TMDs技术的10nm一下工艺的晶圆,还为单分子层的TMD FET建立了一个全新的基准,和相同工艺下的硅晶体管进行横向比较得出:在低的欧姆接触式集成电路大尺度微缩晶体管的关键技术,采用铋(Bi)金属材料能够获得目前最大的通流密度和最小的接触电阻,可满足下一代芯片工艺的技术目标。

国立台湾大学电机系暨光电所吴志毅教授进一步说明,使用铋为接触电极的关键结构后,二维材料晶体管的效能不但与硅基半导体相当,又与目前主流的硅基工艺技术兼容,有助于突破摩尔定律的未来极限。虽然目前仍处于研究阶段,但该成果能为新一代芯片提供省电和高速等优点。

在学术前沿研究领域获得新技术突破的同时,台积电在新一代工艺的研发和量产上也在稳步前行。根据台积电的规划,其3nm工厂已经建成,并正在努力提高产量。乐观估计台积电将在明年完成认证和试生产,并在2022年开始大规模量产。据称自研M1芯片的苹果芯片部门也开始与台积电讨论3nm芯片的订单事宜,有计划将3nm的M系列用于MacBook和iMac系列电脑,从而占据首发优势。

据《电子时报》报道,台积电最近宣布在2nm工艺方面取得重大内部突破,预计在2023年下半年进行风险试生产,并在2024年投入大规模生产。而针对前几天《自然》的论文和绝缘材料提及到的1nm绝缘层,很大程度上是台积电为了2025年实现1nm风险生产做的提前性研究。但是也有观点称,目前各家的GAA和三星MCB还有部分结构和工艺流程问题没有解决,实现真正量产和高良率似乎还有些路要走。三星和台积电目前的3nm也有产能问题,更何况比3nm复杂多倍的2nm量产了。

三星:3nm节点率先转向GAAFET结构

三星的5nm并不是一个新工艺节点,而是其7nm平台的衍生迭代产品。其晶体管密度提高甚至不及台积电的N5,可能也不会高于英特尔的10nm。然而,三星的3nm节点将是一个全新的起点,因为它在业界率先采用MCBFET晶体管结构。该节点现在的目标是2022年进入量产,虽然在尺寸和密度方面没有太大提升,但它可能会在技术和上市时间上取得一定的先发优势。

三星率先推出GAAFET与英特尔2011年推出22nm的FinFET类似,当时FinFET的密度与台积电的平面型28nm相当。尽管三星不会拥有密度优势,但在市场上率先推出GAAFET技术仍将领先台积电约三年。三星在2019年宣布计划在十年内投资超过1000亿美元以赶上台积电,如果其MCBFET技术达到预期,将有助于缩短与台积电的差距。

晶体管结构技术进化图(图源:三星)

基于GAA的FET(GAAFET)有多种形式,大多数研究都是基于纳米线的GAAFET,它们具有较小的沟道宽度。这些类型的GAAFET通常用于低功耗设计,但很难制造出来。另一种实现方式是使沟道像水平铺放的纸一样,通过增加沟道面积来为性能和尺寸带来好处。三星称其基于纳米片的GAAFET为多桥沟道FET或MBCFET。

在本月初举行的线上IEEE国际固态电路会议上,三星工程师展示了其MBCFET结构的灵活性如何以极低的电压实现片上存储单元的写入操作,其电压可以降低数百毫伏,从而有可能大大降低未来芯片的功耗。三星电子副总裁Taejoong Song在会议上表示:“业界使用FinFET晶体管已有十年之久,但是在3纳米工艺中,我们在晶体管四围都使用了栅极包围起来,这种新型晶体管具有高速、低功耗和小尺寸的优点”。

Song及其团队正在利用这种灵活性来提高下一代SRAM性能。SRAM是一种六晶体管存储单元,主要用作处理器上的高速缓存,它也是逻辑芯片封装最密集的部分之一。三星测试了两种方案来提高SRAM的写入电压裕度,这是切换单元状态所需的最低电压。其目的是降低写入SRAM单元所需的电压,而又不会使该单元变得不稳定,以至于其读取会意外翻转。他们提出的两种方案都利用了纳米片沟道宽带Weff的调节灵活性,特别是相对于上拉晶体管加宽了传输栅极晶体管,该单元的写入电压要比现有结构低230 mv。

三星在其首个3GAE工艺设计中做出了许多承诺,其一是将工作电压从0.75伏降低到0.70伏。三星宣布的总体PPA值也令人印象深刻:与7nm相比,3GAE将提供1.35倍的性能,0.5倍的功耗和0.65倍的裸片尺寸。

三星表示,这些性能数字是基于对频率要求较高的芯片设计使用较大宽度的单元,而对省电更为重视的设计可以使用较小宽度的单元。除了3GAE,三星还透露其第二代3nm工艺将称为3GAP,重点是高性能处理能力。3GAP流程将以优化为重点,并利用三星从3GAE中学到的知识。3GAE将于2021年投入风险生产,并有可能在2022年实现量产。

英特尔:2023实现纳米带GAA 5nm,2029年实现1.4nm工艺

在2020年国际VLSI会议上,英特尔CTO Mike Mayberry在其主题演讲中讨论了许多新的制造技术,包括从FinFET扩展到GAA,甚至到2D纳米片结构,最终完全放弃CMOS。Mayberry博士预计纳米线晶体管能够在五年内实现量产,这将为英特尔指明前进的方向。

英特尔将业界通称的GAA称为纳米带(Nanoribbon),虽然还没有像TSMC和三星那样给出明确的GAA规划图,但预计新任CEO将加速英特尔追赶TSMC和三星的步伐。尽管10nm工艺一再拖延,英特尔仍坚信摩尔定律的持续发展,从FinFET向GAA的转换也许是一个很好的契机。

今年英特尔会发布新的工艺节点(7纳米),2022年推出7+版本,然后是2023的7 ++版本,以及一个全新的工艺节点,据信为5nm。照此推断,2024将是5+,然后2025是5 ++和3nm。如果如Mayberry博士说的那样,要在5年内实现大批量生产,我们预期英特尔将在2023-2024年实现5nm的GAA。

在最近举行的IEEE国际电子器件会议(IEDM)上,英特尔展示了一种不同的晶体管堆叠方式:将一对NMOS和PMOS上下堆叠在一起。该方案可有效地将简单CMOS电路的面积减少一半,这意味着未来IC的晶体管密度可能会翻倍。

英特尔工程师首先将这一方案应用于纳米片晶体管结构,并构建了最简单的CMOS逻辑电路--反相器。通过堆叠晶体管并调整互连,这种反相器的面积减少了一半。这一思路是否可行还有待验证,不过其他研究机构和公司也在寻求堆叠纳米片的设计方案,有的将它们称为互补FET或CFET。比利时研究机构Imec率先提出了CFET概念,而台湾的研究人员也发布了一种CFET结构,其中PMOS和NMOS有各自的纳米片。

英特尔发布的未来十年制造路线图。(图片来源:Anandtech)

英特尔将按照每两年一次重大节点升级的节奏进行。我们看到2019年推出了10nm(10nm +),今年将发布7nm,2023年发布5nm(将采用GAA结构),2025年发布3nm,2027年发布2nm,到2029年将发布1.4nm。

结语

10年前英特尔率先研发出采用FinFET结构的22nm工艺,但却没能保持两年更新一代的节奏,逐渐被台积电和三星甩在后面了。台积电将FinFET发挥到了极致,也因为专注和全心的投入而赢得苹果和英伟达等业界巨头的信任。三星一直在追赶,现在把握住了GAAFET这一新型晶体管结构,能否赶上甚至超越台积电就看GAA了。