High-NA EUV光刻机进展顺利

在上个月的SPIE 高级光刻 + 图案化会议上,imec展示了其联合High-NA 实验室的最新成果,以及与ASML合作开发的围绕极紫外 (EUV) 光刻系统的图案化生态系统。

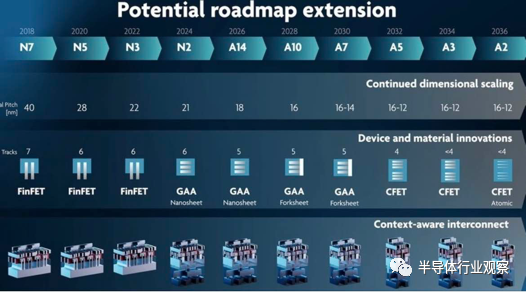

未来的晶体管可能选择

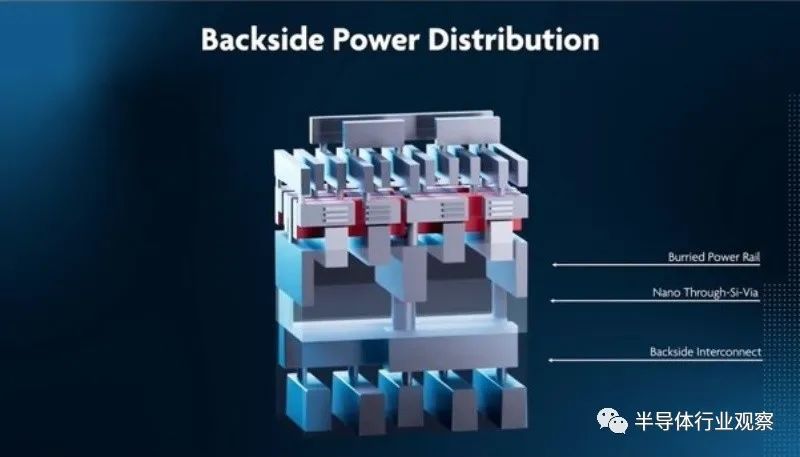

布线和供电也是关键

最靠近硅晶体管的那些层又薄又小,以便连接到微小的晶体管,但是随着您在堆栈中上升到更高级别,它们的尺寸会增加。正是这些具有更广泛互连的级别更擅长提供功率,因为它们具有较小的电阻。

由于晶体管下方有如此多的未使用空间,您可以将 BPR 沟槽做得又宽又深,这非常适合输送电力。与直接位于晶体管顶部的薄金属层相比,BPR 的电阻可以是其 1/20 到 1/30。这意味着 BPR 将有效地允许您为晶体管提供更多功率。

此外,通过将电源轨从晶体管的顶部移开,您可以为信号传输互连腾出空间。这些互连形成基本电路“单元”——最小的电路单元,例如 SRAM 存储器位单元或我们用来组成更复杂电路的简单逻辑。通过使用我们腾出的空间,可以将这些单元缩小16% 或更多,这最终可以转化为每个芯片上更多的晶体管。即使特征尺寸保持不变,进一步推动摩尔定律。

写在最后