CA168首页 >

自动化信息 >

综合信息 > 信息详情

三星宣布新晶体管:1nm后的选择?

IBM 和三星声称他们在半导体设计方面取得了突破。在旧金山 IEDM 会议的第一天,两家公司公布了一种在芯片上垂直堆叠晶体管的新设计。对于当前的处理器和 SoC,晶体管平放在硅表面上,然后电流从一侧流向另一侧。相比之下,垂直传输场效应晶体管 (VTFET) 彼此垂直,电流垂直流动。据 IBM 和三星称,这种设计有两个优点。首先,它将允许他们绕过许多性能限制,将摩尔定律扩展到 1 纳米阈值之外。更重要的是,由于电流更大,该设计减少了能源浪费。他们估计 VTFET 将使处理器的速度比采用 FinFET 晶体管设计的芯片快两倍,功耗降低 85%。IBM 和三星声称,这一过程可能有朝一日允许手机一次充电使用整整一周。他们表示,它还可以使某些能源密集型任务(包括加密采矿)更加节能,因此对环境的影响较小。IBM 和三星尚未透露他们计划何时将该设计商业化。他们并不是唯一一家试图突破 1 纳米屏障的公司。英特尔在七月曾表示,它的目标是到 2024 年完成埃级芯片的设计。该公司计划使用其新的“英特尔 20A”节点和 RibbonFET 晶体管来完成这一壮举。

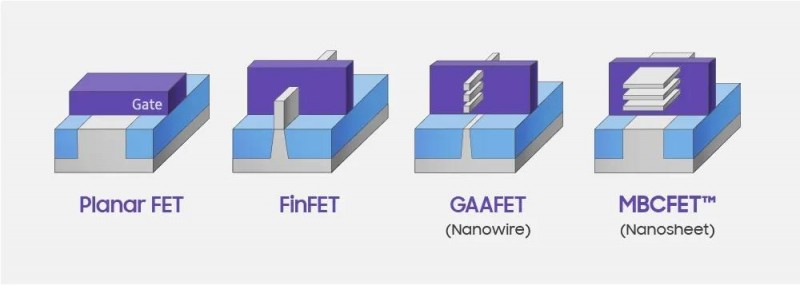

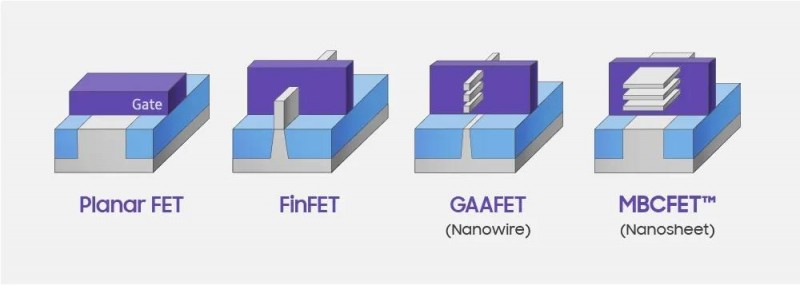

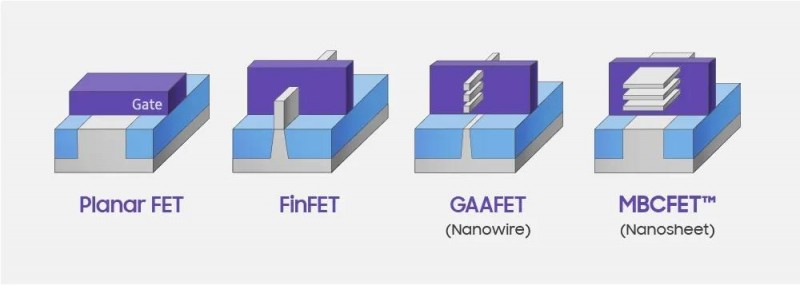

在先进半导体工艺上,台积电目前是无可争议的老大,Q3季度占据全然53%的晶圆代工份额,三星位列第二,但份额只有台积电的1/3,所以三星押注了下一代工艺,包括3nm及未来的2nm工艺。根据三星的计划,3nm工艺会放弃FinFET晶体管技术,转向GAA环绕栅极,3nm工艺上分为两个版本,其中3GAE(低功耗版)将在2022年年初投入量产,3GAP(高性能版)则会在2023年年初批量生产。对比5nm,三星新的3nm GAA可以让面积缩小35%,同功耗下性能提高30%,同性能下功耗降低50%。再往后就是2nm工艺,三星高管日前再次表态2nm工艺会在2025年量产。

不过具体的工艺指标还没公布,只知道还是GAA晶体管,跟3nm一样基于MBCFET(多桥沟道FET)技术,这是一种纳米片晶体管,可以垂直堆叠,而且兼容现在的CMOS工艺,共享设备与制造方法,降低了新技术的升级成本。三星的2nm工艺是一大进步,创新亮点不少,而且跟现在已有的2nm技术不同——此前IBM全球首发了2nm芯片,指甲盖大小的面积就可以集成500亿晶体管,相比7nm工艺提升了45%的性能或者减少75%的功耗,预计2024年量产。三星也参与了IBM的2nm技术,然而自己量产的2nm技术跟IBM的2nm并不一样,后者需要新的生产方法,三星还会依赖自家研发的2nm技术。