DFM

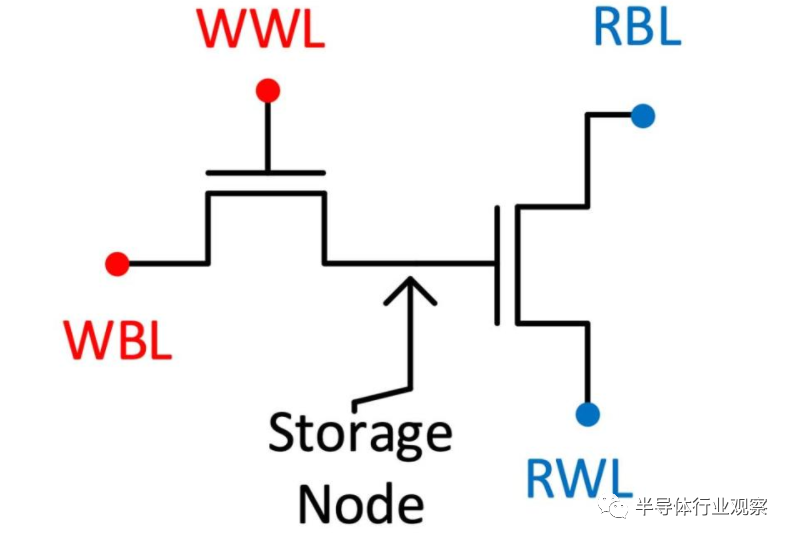

2T0C DRAM

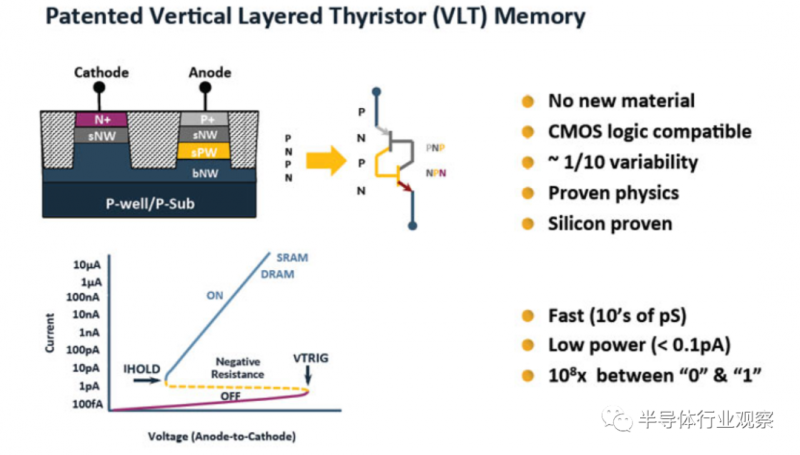

VLT技术

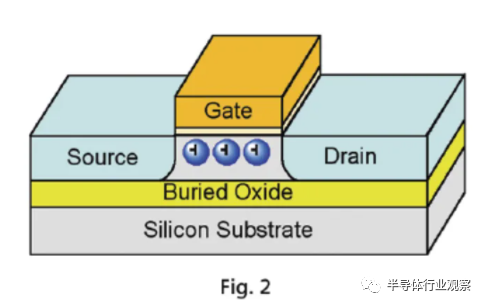

Z-RAM

另外一种途径

这是一个单晶体管,无电容器的DRAM cell,它使用晶体管主体作为一种电容器,其中的电荷(在这种情况下为空穴)被临时存储在其中。电子空穴从晶体管主体的注入和抽出使得能够调节晶体管的静电行为,从而导致两个不同的电流水平。像InGaAs这样的III-V材料通常具有比硅更小的带隙,而硅原则上具有在低得多的电压下工作的潜在优势。反过来,这转化为可能更低的功耗。

IBM方便表示,他们已经证明了无电容器MSDRAM cell的栅极长度为14纳米的可行性。通过使用晶体管本体来存储电子空穴数量,我们能够获得对应于二进制状态0和1的两个不同的电流电平。而该存储器概念的实验实现证实了TCAD仿真获得的结果。

与基于硅的实现相比,IBM使用InGaAs的新颖概念为实现DRAM存储器的积极小型化提供了一条有希望的途径,同时还降低了功耗。从有关性能指标(例如保留时间)的这一概念进一步改进的潜力,而IBM艰辛存在可行的策略来实现这些改进。