在信息时代,数据处理速度的不断提升迫使我们面对一个巨大的挑战:晶体管的密度已经达到了令人难以置信的水平,这些微小的数字开关产生的热量比以往任何时候都要多。

尽管表面上看似容易管理,但实际上,这引发了一系列全行业都需共同解决的新问题——从EDA公司、工艺设备制造商、晶圆厂、封装厂、到现场级监控和分析提供商、材料供应商、研究小组等。

新技术带来的挑战

近年来,持续关注将更多晶体管封装到固定区域,以及与泄漏功率的斗争成为了行业的焦点。

然而,每一个新的节点都带来了一系列需要解决的新问题。例如,环栅FET和复合FET等新的晶体管结构变革,虽然为性能提升带来了希望,但也给设计、计量、检查和测试带来了更大的挑战和成本。

● 热量与功耗的挑战:电源问题,尤其是热量问题,正是制约了当今芯片和系统设计的关键因素。持续增加的晶体管密度导致了更高的功率密度,这限制了时钟频率的提升。

因此,许多重要的改进都集中在晶体管本身的外围技术上,如硬件-软件协同设计、更快的物理层和互连、新材料的使用以及更稀疏的算法等。

● 功耗密度与时钟频率的制约:随着晶体管密度的增加,功耗密度也相应增加,从而限制了时钟频率的提高。

因此,必须寻找外围技术的改进,例如硬件-软件协同设计、更快的PHY和互连、新材料用于绝缘和电子迁移率、更稀疏的算法等。

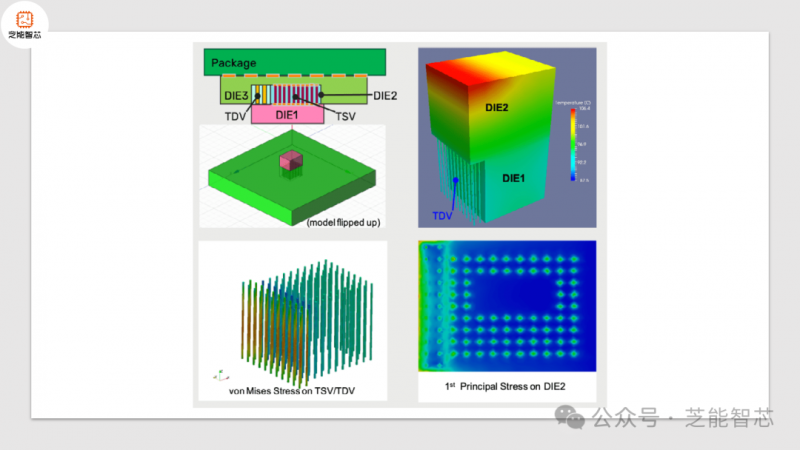

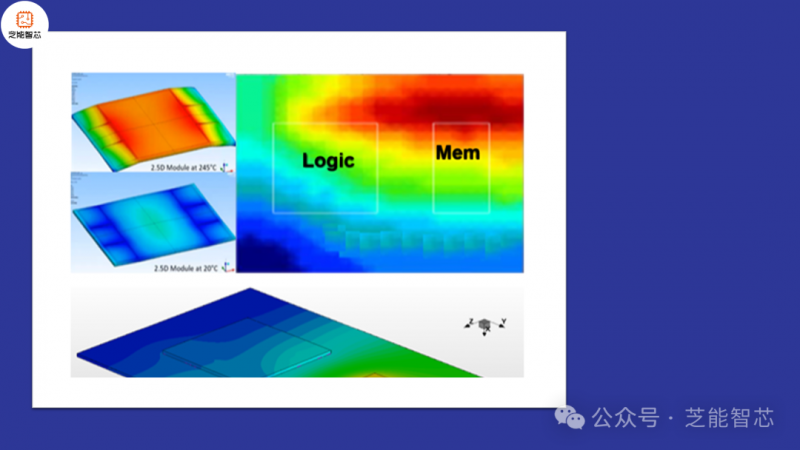

● 动态热梯度与热应力:在高密度芯片和封装中,动态热梯度成为一个令人担忧的问题。瞬态热梯度的不可预测性和变化性,可能导致热应力,进而影响芯片的可靠性和性能。

● 热量带来的问题:热量不仅影响系统的性能,还可能导致一系列难以预测的问题。从电介质的击穿、电迁移、到内存运行速度的降低,以及噪声对信号完整性的影响,这些问题无一不在缩短芯片的寿命。

应对策略

电力问题没有单一解决方案,但有很多局部解决方案。

● 限制过度设计,即根据目标用例确定必要功能,避免不必要的功能增加。

● 在设计中考虑实际工作负载,以确保电力覆盖范围足够。

● 背面供电是一种选择,特别是在最先进的节点上,可以减少功耗。

● 利用芯片和封装内部的传感器来监测电源行为的变化也是一种方法。

● 通过优化TSV布局和使用散热通孔等方法,将热量传导到可以散热的地方,可以有效减轻热量问题。

电源问题与芯片的架构、布局布线、信号完整性、热量、可靠性、可制造性和老化密切相关。解决这些问题需要整个行业共同努力,学会处理或解决与功率相关的各种影响。

行业需要更好地理解完整的系统堆栈,并采取相应的措施。针对瞬态热梯度的建模和分析可以帮助工程师们更好地预测和解决问题。对于晶体管的新结构和工艺,需要不断创新并加强模拟和测试手段,以应对可能的问题。从限制过度设计到在设计上运行实际工作负载,从背面供电到利用传感器监测与电源相关的行为的变化,都是应对电源问题的方法。

随着技术的不断进步,电源设计面临的挑战也在不断增加。解决这些挑战需要全行业的共同努力和持续创新,以确保芯片和系统的稳定运行,为信息社会的发展提供可靠的支持。

通过全面了解电源问题的本质,并采取合适的措施,我们可以为未来的芯片设计铺平道路,使其更加高效、可靠和可持续。