据财讯网报道,美中对抗下,半导体产业受高度重视,但风光一时的日本于台韩势力崛起后,产业全球市占率仅9% 左右。为避免日本擅长的材料、设备等产业随客户到美国设厂,导致日本产业空洞化,日本经济产业省积极邀请台积电到日本设厂。

半导体前段制程,已达极限

擅长研发材料,日本找利基

台积电为什么聚焦先进封装

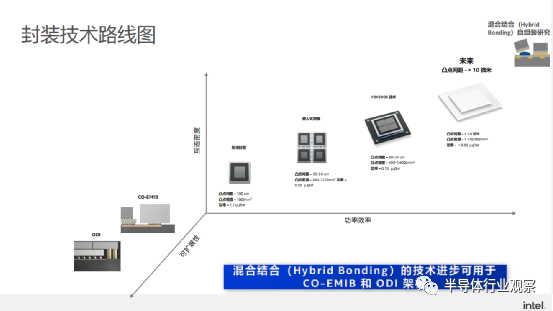

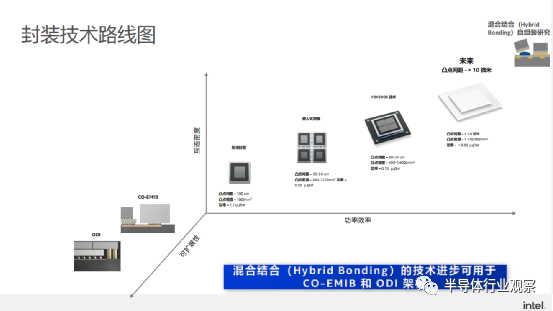

Intel的封装路线图

力抗台积电!三星宣布I-Cube4 先进封装芯片即将上市

半导体前段制程,已达极限

擅长研发材料,日本找利基

台积电为什么聚焦先进封装

Intel的封装路线图

力抗台积电!三星宣布I-Cube4 先进封装芯片即将上市

下一篇:华为带给中国企业的几点启示

本文仅代表作者个人观点,与中自网无关。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容!来源网络如有误有侵权则删。