CA168首页 >

自动化信息 >

综合信息 > 信息详情

台积电最新N4X工艺解读:在高压下具有极高性能

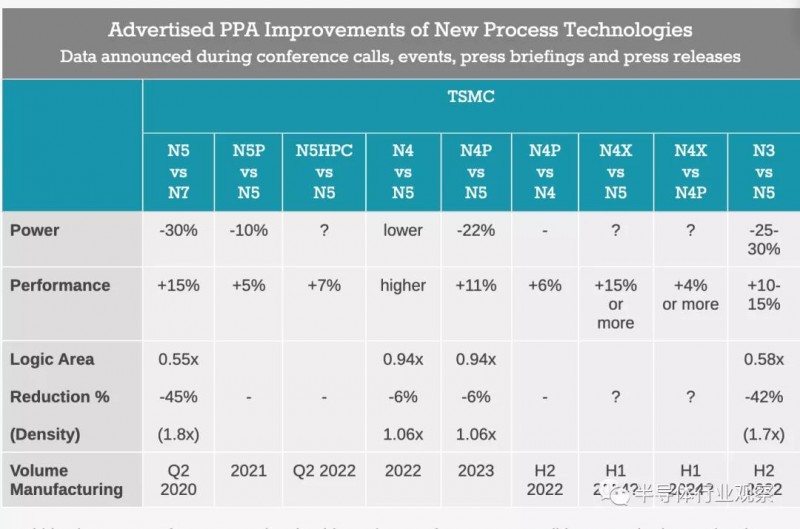

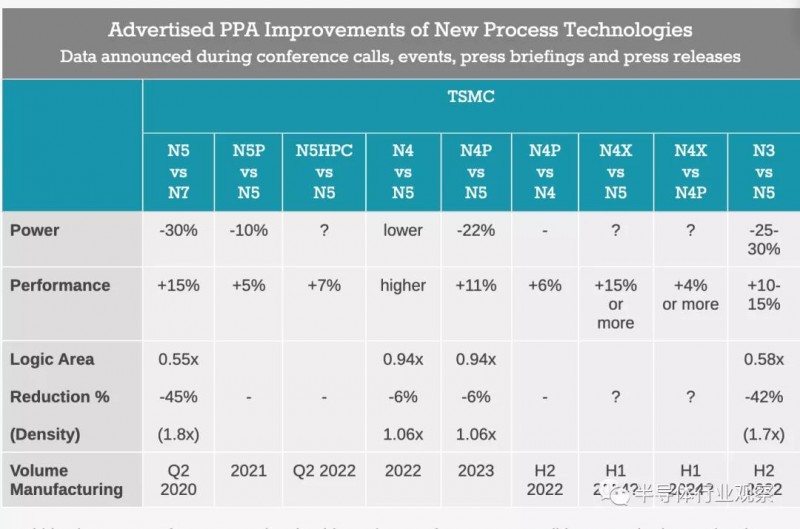

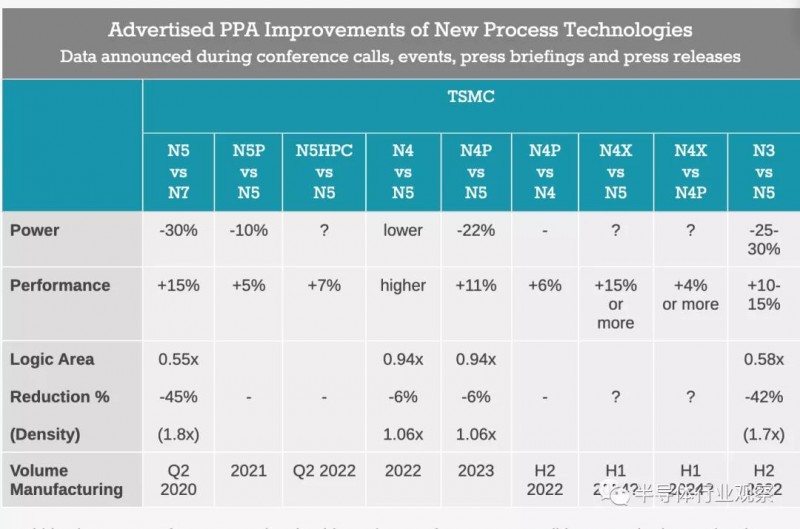

上周,台积电宣布了一种专为高性能计算 (HPC) 产品量身定制的新制造工艺N4X。台积电承诺,新工艺将与台积电 N5 系列节点的晶体管密度和设计规则与以超高电压驱动芯片以实现更高频率的能力相结合,这对服务器 CPU 和 SoC 尤其有用。有趣的是,台积电的 N4X 甚至可以实现比该公司下一代 N3 工艺更高的频率。众所周知,过去多年,晶体管尺寸缩小引起的问题之一是其触点尺寸缩小,这意味着接触电阻增加,从而导致功率传输出现问题。不同的制造商使用不同的方法来解决接触电阻问题:英特尔使用钴触点而不是钨触点,而其他制造商选择使用选择性钨沉积形成触点技术。虽然这些方法几乎适用于所有类型的芯片,但仍有一些方法可以进一步改善高性能计算 (HPC) 设计的功率传输,这些设计对于所使用的功率/电压的总和相对不适度。这正是台积电对其 N4X 节点所做的。但在我们继续详细介绍新的制造工艺之前,让我们先看看台积电承诺的优势。台积电声称,与使用 N5 制造的类似电路相比,其 N4X 节点的时钟频率最高可提高 15%,与使用其 N4P 节点生产的 IC 相比,在 1.2V 下运行时的频率最高可提高 4%。此外——而且似乎更重要的是——N4X 可以实现超过 1.2V 的驱动电压,以获得更高的时钟。将数字放在上下文中:在 N5 上制造的 Apple M1 系列 SoC 以 3.20 GHz 运行,但如果这些 SoC 是使用 N4X 生产的,那么使用台积电的数学计算,它们理论上可以被推到 3.70 GHz 左右或更高的频率,电压超过1.2V。报道指出,台积电不会将 N4X 的晶体管密度与其 N5 系列的其他成员进行比较,但通常用于 HPC 应用的处理器和 SoC 不是使用高密度库设计的。至于电源,与使用其他 N5 级节点生产的芯片相比,超过 1.2V 的驱动电压自然会增加功耗,但由于该节点是为 HPC/数据中心应用而设计的,因此它的重点是提供尽可能高的性能,功耗反而是次要问题。事实上,过去几代 HPC 级 GPU 和类似部件的总功耗一直在增加,而且没有迹象表明这种情况会在未来几代产品中停止,这在一定程度上要归功于 N4X。台积电业务发展高级副总裁 Kevin Zhang 博士表示:“HPC 现在是台积电增长最快的业务部门,我们很自豪地推出 N4X,这是我们超高性能半导体技术‘X’系列中的第一个。“高性能计算领域的需求是无情的,台积电不仅定制了我们的‘X’半导体技术以释放终极性能,而且还将其与我们的 3DFabric 先进封装技术相结合,以提供最佳的高性能计算平台。”为了提高性能并使超过 1.2V 的驱动电压成为可能,台积电必须改进整个工艺堆栈。首先,它重新设计了 FinFET 晶体管,并针对高时钟和高驱动电流对它们进行了优化,这可能意味着降低电阻和寄生电容并提高流过通道的电流。我们不知道它是否必须增加栅到栅间距,此时台积电没有说明它究竟做了什么以及它如何影响晶体管密度。其次,它引入了新的高密度金属-绝缘体-金属 (MiM) 电容器,可在极端负载下稳定供电。第三,它重新设计了后端金属堆栈,为晶体管提供更多功率。同样,我们不知道这如何影响晶体管密度和最终的芯片尺寸。在很大程度上,英特尔为其 10纳米增强型 SuperFin(现在称为英特尔 7)工艺技术引入了类似的增强功能,这并不奇怪,因为这些是提高频率潜力的自然方法。令人惊叹的是,随着时间的推移,台积电如何显着提高其 N5 技术的时钟速度潜力。15% 的增长使 N4X 接近其下一代 N3 制造技术。同时,由于驱动电压超过 1.2V,该节点实际上将启用比 N3 更高的时钟,使其特别适合数据中心 CPU。台积电表示,预计首批 N4X 设计将在 2023 年上半年进入风险生产阶段,这是对时间的非常模糊的描述,因为这可能意味着非常晚的 2022 年或 2023 年初。无论如何,通常需要一年时间才能完成芯片从风险生产到大批量生产迭代,因此预计首批 N4X 设计将在 2024 年初投放市场是合理的。N4X 有望在时钟方面具有优势,而 N3 将在晶体管密度方面具有主要优势。